Question

You will type the first two digits of your student number (you will also experiment with other digits) using your own keyboard and the Logisim

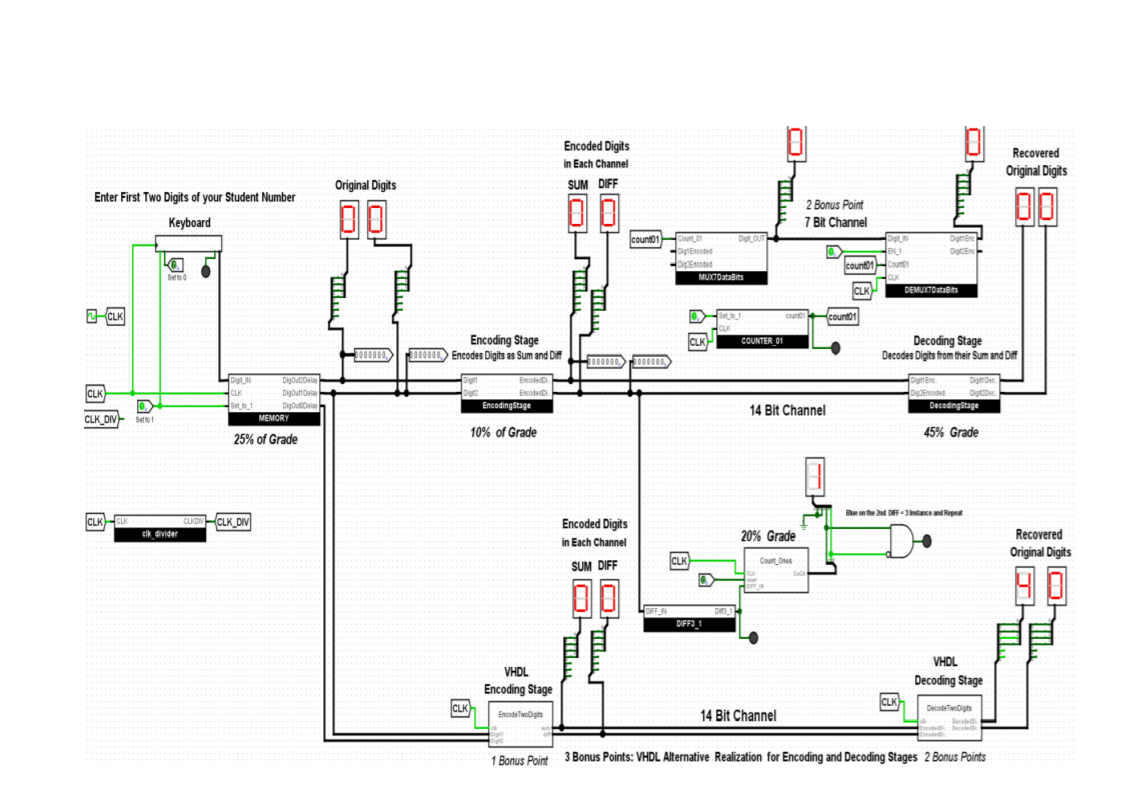

You will type the first two digits of your student number (you will also experiment with other digits) using your own keyboard and the Logisim keyboard block. Each digit will be converted to a 7 bit ascii representation by the Logisim keyboard. You should encode the two digits typed in your keyboard as their sum and their difference. You will send the encoded version (sum and diff) of the two digits, simultaneously, through a 14 bit channel (35% of grade up to this part). At the other end of the channel you will decode the originals digits of you student number from the arriving sum and difference of such digits (this particular part is 45 % of your grade). In addition, when experimenting with streams of different digits typed at the keyboard, a blue light should be turned on after two instances, consecutive or not consecutive, where the difference between the digits was 3. The blue light will remain on until another instance of 3, being the difference between the digits, occurs. It will basically count two instances of the difference between digits being 3 and will repeat the count (20% of grade). The keyboard will be used in Logisim as it was shown in class or in the class videos. A demonstration video of what is expected will also be made available in the Project Folder in Blackboard. Constraint: Do not use more than 5 Flip Flops. You may use Logisim blocks for arithmetic operations or you can design you own sub-circuits. VHDL Bonuses (all bonus points are over the final course grade): A VHDL realization of the encoding stage that outputs the sum and difference of the first two digits is worth 1 Bonus Point. A VHDL realization of the decoding stage that recovers the original digits from their sum and difference is worth 2 Bonus Points. Other Bonus: A Multiplexer-Demultiplexer design that allows to transmit one digit at a time over a 7 bit channel (instead of two digits simultaneously over a 14 bit channel) is worth 2 Bonus Points. Note that after the multiplexed channel you should be able to inject the digits in the same decoding block used for the 14 bit channel. This is worth 2 Bonus points.

I dont understand how to make the encoding stage and the count_one stage. (you dont have to solve the bonus, only the four circuits that have a percentage). (prefers answer through logisim) (student #: 34)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started