Design the circuit in Figure 13.2 such that the maximum power dissipated in the circuit is (15

Question:

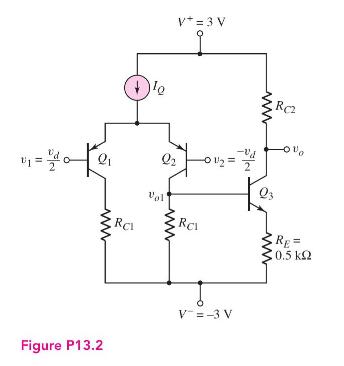

Design the circuit in Figure 13.2 such that the maximum power dissipated in the circuit is \(15 \mathrm{~mW}\) and such that the common-mode input voltage is in the range \(-3 \leq v_{C M} \leq 3 \mathrm{~V}\). Using a computer simulation, adjust the value of \(R_{3}\) such that the output voltage is zero for zero input signal voltages.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: