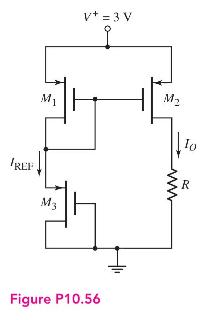

The circuit in Figure P10.56 is a PMOS version of a two-transistor MOS current mirror. Assume transistor

Question:

The circuit in Figure P10.56 is a PMOS version of a two-transistor MOS current mirror. Assume transistor parameters of \(V_{T P}=-0.4 \mathrm{~V}\), \(k_{p}^{\prime}=60 \mu \mathrm{A} / \mathrm{V}^{2}\), and \(\lambda=0\). The transistor width-to-length ratios are \((W / L)_{1}=25,(W / L)_{2}=15\), and \((W / L)_{3}=5\).

(a) Determine \(I_{O}, I_{\mathrm{REF}}\), \(V_{S G 1}\), and \(V_{S G 3}\).

(b) What is the largest value of \(R\) such that \(M_{2}\) remains biased in the saturation region?

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: