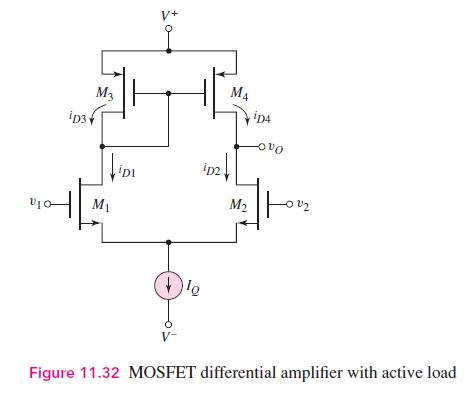

The circuit parameters for the diff-amp shown in Figure 11.32 are (V^{+}=1.8 mathrm{~V}, V^{-}=-1.8 mathrm{~V}), and (I_{Q}=120

Question:

The circuit parameters for the diff-amp shown in Figure 11.32 are \(V^{+}=1.8 \mathrm{~V}, V^{-}=-1.8 \mathrm{~V}\), and \(I_{Q}=120 \mu \mathrm{A}\). The NMOS transistor parameters are \(V_{T N}=0.3 \mathrm{~V}, k_{n}^{\prime}=100 \mu \mathrm{A} / \mathrm{V}^{2},(W / L)_{n}=8\), and \(\lambda_{n}=\) \(0.025 \mathrm{~V}^{-1}\). The parameters of the PMOS transistors are \(V_{T P}=-0.3 \mathrm{~V}\), \(k_{p}^{\prime}=40 \mu \mathrm{A} / \mathrm{V}^{2},(W / L)_{p}=10\), and \(\lambda_{p}=0.04 \mathrm{~V}^{-1}\).

(a) Determine the small-signal differential-mode voltage gain \(A_{d}=v_{o} / v_{d}\).

(b) What is the maximum common-mode voltage gain that can be applied such that all transistors are still biased in the saturation region?

Step by Step Answer:

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen