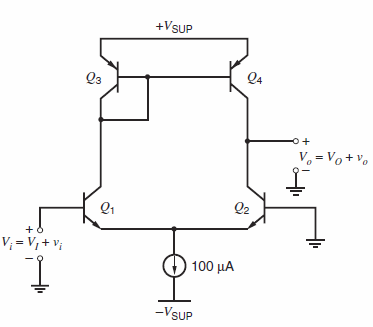

Determine the worst-case input offset voltage for the circuit of Fig. 4.58. Assume the worst-case I S

Question:

Fig. 4.58:

Transcribed Image Text:

+VSUP Q4 Q3 V, = Vo+v, Q2 +6 V; = V, + v; 100 μΑ -VSUP

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 75% (8 reviews)

From 4315 Wor...View the full answer

Answered By

PALASH JHANWAR

I am a Chartered Accountant with AIR 45 in CA - IPCC. I am a Merit Holder ( B.Com ). The following is my educational details.

PLEASE ACCESS MY RESUME FROM THE FOLLOWING LINK: https://drive.google.com/file/d/1hYR1uch-ff6MRC_cDB07K6VqY9kQ3SFL/view?usp=sharing

3.80+

3+ Reviews

10+ Question Solved

Related Book For

Analysis and Design of Analog Integrated Circuits

ISBN: 978-0470245996

5th edition

Authors: Paul R. Gray, Paul J. Hurst Stephen H. Lewis, Robert G. Meyer

Question Posted:

Students also viewed these Physics questions

-

Repeat Problem 4.38, but assume that 2-kΩ resistors are placed in series with the emitters of Q 3 and Q 4 . Assume the worst-case resistor mismatch is ± 0.5 percent and the...

-

Repeat Problem 4.38 but replace the bipolar transistors with MOS transistors as in Problem 4.14. Assume the worst-case W/L mismatches in the transistors are ± 5 percent and the worst-case V t...

-

(a) Calculate the random input offset voltage for the op amp in Fig. 6.16. Assume the matching is perfect except thatV t3 V t4 = 10mV. Also assume that all transistors have equal W/Land operate in...

-

Match the accounting terminology to the definitions. 1. Sarbanes-Oxley Act 2. Internal control 3. Encryption 4. Separation of duties 5. Internal auditors

-

On a recent scuba dive, Mr. UW located a shipwreck and recovered a Spanish sword inlaid with precious stones. The sword's appraised value is $11,500. Mr. UW mounted the sword over his fireplace....

-

At the beginning of the school term, what type of account is the tuition that your college or university collects from students?

-

Researching Consumer Purchases. Using the consumer buying matrix, analyze a consumer purchase you plan to make in the future. What factors affected the selection of the attributes and weights you...

-

(Time Value Concepts Applied to Solve Business Problems) Answer the following questions related to Mark Grace Inc. (a) Mark Grace Inc. has $572,000 to invest. The company is trying to decide between...

-

The normal balance of asset is Debit CrediCredit

-

Jay Rexford, president of Photo Artistry Company, was just concluding a budget meeting with his senior staff. It was November of 20x4, and the group was discussing preparation of the firms master...

-

A pair of bipolar current sources is to be designed to produce output currents that match with 1 percent. If resistors display a worst-case mismatch of 0.5 percent, and transistors a worst-case V...

-

A circuit as shown in Fig. 5.1 has V CC = 15V, R 1 = R 2 = 0, R 3 = 5k¦, R L = 2k¦, V CE(sat) = 0.2 V, and V BE(on) = 0.7 V. All device areas are equal. (a). Sketch the transfer...

-

(a) Do the CC bond lengths in benzene alternate shortlong-short-long around the ring? Why or why not? (b) Are CC bond lengths in benzene shorter than CC single bonds? (c) Are CC bond lengths in...

-

Companies that invest heavily in eco-friendly initiatives, such as transitioning to renewable energy sources or implementing carbon offset programs, may initially face increased operational costs....

-

Answer each question individually please. 14-13 What are the advantages and drawbacks of universities using social media to communicate with various stakeholdersstudents, potential students, alumni,...

-

act as a consultant hired by the operations director of the Barry Computer Company provide a financial analysis and comparison to the industry. You will conduct a financial ratio analysis to gain a...

-

Building a sense of community is not just a moral thing to do, but also a pragmatic one. In today's competitive and ever-evolving business environment, the organizations that can attract the most...

-

Watch https://youtu.be/U3MtvvNjUR4 What do you think of Dr. Saint's ideas about barriers to change? What do you think about social learning? Could this tool be used to make real change? How can the...

-

Differentiate the functions in Problems. Assume that A, B, and C are constants. f(t) = Ae t + B ln t

-

Tell whether the angles or sides are corresponding angles, corresponding sides, or neither. AC and JK

-

A small wooden block with mass 0.800 kg is suspended from the lower end of a light cord that is 1.60 m long. The block is initially at rest. A bullet with mass 12.0 g is fired at the block with a...

-

A 5.00-kg chunk of ice is sliding at 12.0 m/s on the floor of an ice-covered valley when it collides with and sticks to another 5.00-kg chunk of ice that is initially at rest. Since the valley is...

-

(a) When an object is in a circular orbit of radius r around the earth (mass ), the period of the orbit is T, given by Eq. (13.12), and the orbital speed is given by Eq. (13.10). Show that when the...

-

Problem 12.6A (Algo) Liquidation of a partnership LO P5 Kendra, Cogley, and Mel share income and loss in a 3.21 ratio (in ratio form: Kendra, 3/6: Cogley, 2/6; and Mel, 1/6), The partners have...

-

Melody Property Limited owns a right to use land together with a building from 2000 to 2046, and the carrying amount of the property was $5 million with a revaluation surplus of $2 million at the end...

-

Famas Llamas has a weighted average cost of capital of 9.1 percent. The companys cost of equity is 12.6 percent, and its cost of debt is 7.2 percent. The tax rate is 25 percent. What is the companys...

Study smarter with the SolutionInn App