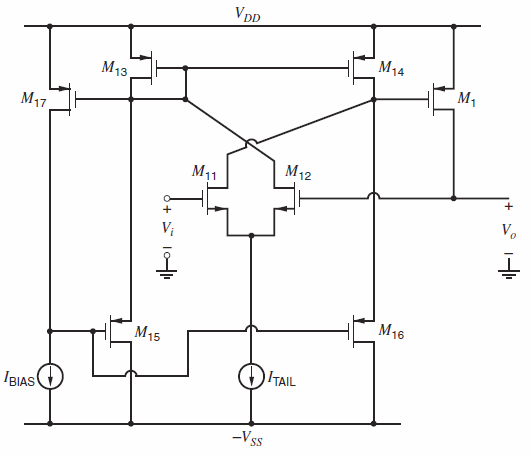

Using the schematics from Fig. 5.35 and Problem 5.24, design the output stage shown in Fig. 5.32

Question:

(a) VDD = VSS = 2.5 V.

(b) The standby power dissipation should be no more than 70 mW.

(c) RL = 100 Ω.

(d) The maximum allowed gain error with zero offsets and all transistors operating in the active region is 1 percent.

(e) In Fig. 5.35,(W/L)17 = (W/L)1/100 and (W/L)13 = (W/L)14 = (W/L)1/10. Similarly, in Problem 5.24, (W/L)27 = (W/L)2/100 and (W/L)23 =(W/L)24 = (W/L)2/10.

(f) To control the quiescent current, the maximum allowed error-amplifier gain is 5.

(g) Your solution is allowed to use four ideal current sources, two in each error amplifier. To allow these ideal current sources to be replaced by real transistors in a design step not required in this problem, the voltage across each ideal current source in Fig. 5.35 must be at least 0.5 V when Vo ‰¥ 0. Similarly, the voltage across each ideal current source in the complementary circuit from Problem 5.24 must be at least 0.5 V when Vo ‰¤ 0.

(h) To guarantee that M16 and M26 do not cut off under these conditions, assume ITAIL = 5 IBIAS in Fig. 5.35 and ITAILP = 5 IBIASP in Problem 5.24.

(i) For both n- and p-channel transistors, assume that λ = 0, Ld = Xd = 0, and ignore the body effect. Use Ldrwn = 1 µm for all transistors, and use Table 2.3 for other transistor parameters.

(j) The distortion of the output stage should be minimized under the above conditions.

Verify your design using SPICE.

Figure 5.35:

Figure 5.32:

Step by Step Answer:

Analysis and Design of Analog Integrated Circuits

ISBN: 978-0470245996

5th edition

Authors: Paul R. Gray, Paul J. Hurst Stephen H. Lewis, Robert G. Meyer