Assume both benchmarks have a base CPI of 1 (ideal L2 cache). If having non-blocking cache improves

Question:

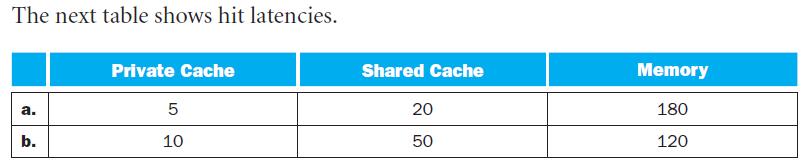

Assume both benchmarks have a base CPI of 1 (ideal L2 cache). If having non-blocking cache improves the average number of concurrent L2 misses from 1 to 2, how much performance improvement does this provide over a shared L2 cache? How much improvement can be achieved over private L2?

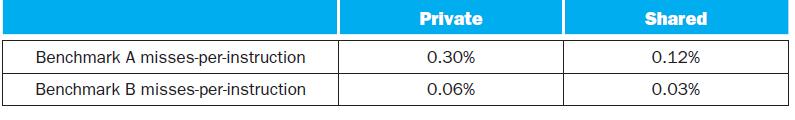

Both Barcelona and Nehalem are chip multiprocessors (CMPs), having multiple cores and their caches on a single chip. CMP on-chip L2 cache design has interesting trade-offs. The following table shows the miss rates and hit latencies for two benchmarks with private vs. shared L2 cache designs. Assume L1 cache misses once every 32 instructions.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy

Question Posted: