Question: For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we change

For this problem, assume that all branches are perfectly predicted (this eliminates all control hazards) and that no delay slots are used. If we change load/store instructions to use a register (without an offset) as the address, these instructions no longer need to use the ALU. As a result, MEM and EX stages can be overlapped and the pipeline has only 4 stages. Change this code to accommodate this changed ISA. Assuming this change does not affect clock cycle time, what speedup is achieved in this instruction sequence?

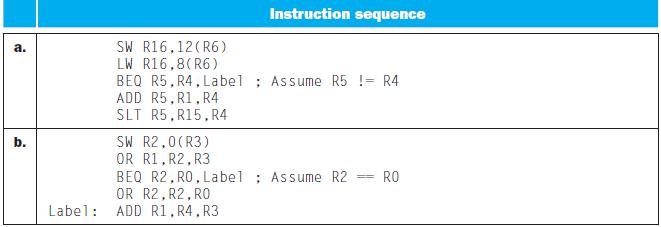

In this exercise, we examine how resource hazards, control hazards, and ISA design can affect pipelined execution. Problems in this exercise refer to the following fragment of MIPS code:

a. b. Label: Instruction sequence SW R16,12(R6) LW R16,8(R6) BEQ R5, R4, Label; Assume R5 != R4 ADD R5, R1, R4 SLT R5, R15, R4 SW R2,0 (R3) OR R1, R2, R3 BEQ R2, RO, Label; Assume R2 OR R2, R2, RO ADD R1, R4, R3. = RO

Step by Step Solution

3.41 Rating (157 Votes )

There are 3 Steps involved in it

Given that loadstore instructions now use a register without an offset as the address and that the M... View full answer

Get step-by-step solutions from verified subject matter experts