It is necessary to design a pipeline for a fixed-point multiplier that multiplies two 8-bit binary integers.

Question:

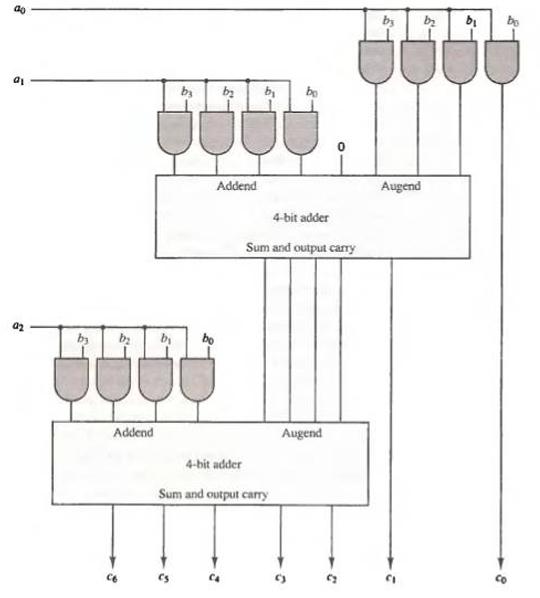

It is necessary to design a pipeline for a fixed-point multiplier that multiplies two 8-bit binary integers. Each segment consists of a number of AND gates and a binary adder similar to an array multiplier as shown in Fig. 10-10.

a. How many AND gates are there in each segment, and what size of adder is needed?

b. How many segments are there in the pipeline?

c. If the propagation delay in each segment is 30 ns, what is the average time that it takes to multiply two fixed-point numbers in the pipeline?

Fig. 10-10

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Question Posted: