The bus system of Fig. 8-2 has the following propagation delay times: 30 ns for the signals

Question:

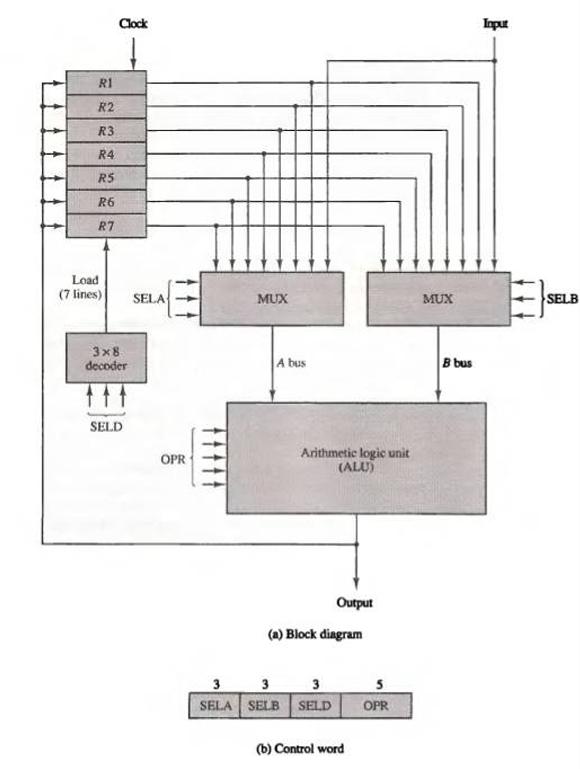

The bus system of Fig. 8-2 has the following propagation delay times: 30 ns for the signals to propagate through the multiplexers, 80 ns to perform the ADD operation in the ALU, 20 ns delay in the destination decoder, and 10 ns to clock the data into the destination register. What is the minimum cycle time that can be used for the clock?

Fig. 8-2

Transcribed Image Text:

R1 R2 R3 R4 R5 R6 R7 Load (7 lines) Clock 3x8 decoder SELD SELA OPR | | | | | MUX A bus Arithmetic logic unit (ALU) Output (a) Block diagram 3 3 3 SELA SELB SELD (b) Control word 5 OPR MUX 8 bus Input SELB

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 75% (4 reviews)

To determine the minimum cycle time for the clock of the bus system we need to consider the sum of t...View the full answer

Answered By

Mario Alvarez

I teach Statistics and Probability for students of my university ( Univerisity Centroamerican Jose Simeon Canas) in my free time and when students ask for me, I prepare and teach students that are in courses of Statistics and Probability. Also I teach students of the University Francisco Gavidia and Universidad of El Salvador that need help in some topics about Statistics, Probability, Math, Calculus. I love teaching Statistics and Probability! Why me?

** I have experience in Statistics and Probability topics for middle school, high school and university.

** I always want to share my knowledge with my students and have a great relationship with them.

** I have experience working with students online.

** I am very patient with my students and highly committed with them

5.00+

1+ Reviews

10+ Question Solved

Related Book For

Question Posted:

Students also viewed these Computer science questions

-

Planning is one of the most important management functions in any business. A front office managers first step in planning should involve determine the departments goals. Planning also includes...

-

The pipeline of Fig. 9-2 has the following propagation times: 40 ns for the operands to be read from memory into registers R1 and R2, 45 ns for the signal to propagate through the multiplier, 5 ns...

-

The state tax department wants to set up what would amount to a series of identical production lines (running 8 hours a day) for processing state tax returns that are submitted on the state's "EZ"...

-

The cylinder in the figure has a radius of 2 ft and rolls without slipping on the horizontal surface. The bar AB is attached to the periphery of the cylinder by a pin at point A. The other end of the...

-

What is the intrinsic value of a put option? How do we interpret this value?

-

The income statement for Astro Inc. for 2010 is as follows: For the Year Ended December 31, 2010 Sales revenue ........... $ 500,000 Cost of goods sold ......... 400,000 Gross profit ........... $...

-

37. Explain why percentage depletion has been referred to as a government subsidy.

-

Hayes Industries purchased the following assets and constructed a building as well. All this was done during the current year. Assets 1 and 2: These assets were purchased as a lump sum for $100,000...

-

Beths Bagels has 6 employees who are paid $24 per hour. At December 31, 2019, each of Bonnies employees had worked 18 hours which had not been paid or recorded. Prior to adjustments, the companys...

-

Specify the control word that must be applied to the processor of Fig. 8-2 to implement the following microoperations. a. R1R2 + R3 b. R4R4 c. R5R5 - 1 d. R6input Fig. 8-2 R1 R2 R3 R4 R5 R6 R7 Load...

-

A bus-organized CPU similar to Fig. 8-2 has 16 registers with 32 bits in each, an ALU, and a destination decoder. a. How many multiplexers are there in the A bus, and what is the size of each...

-

Determine whether the statement is true or false. If it is true, explain why. If it is false, explain why or give an example that disproves the statement. If (t) = 0 for all t, the curve is a...

-

2024 Mathematics 31 Assignment #3 LIMITS 1. Determine the following limits using substitution, then using an algebraic approach if necessary. (Assume trig limits are in radians unless stated...

-

Smitty had a duty of select answerto HaileyThis duty required Smitty to act as select answer would act. A reasonable accountant select answer familiar with tax rules and regulations when asked to...

-

Paul Krugman is an American economist and Nobel laureate. He is also an op-ed columnist and blogger for the New York Times. In June 2011, Paul Krugman declared that a new war would solve the nation's...

-

The Penn State Math Department's total costs in dollars for producing x units of their award winning calculus tutorial videos is 44x C(x) = 300 24x5 1-4x5 x + 73x-13 What is the limiting value of the...

-

Complete the general form equation of the parabola that passes through (1,-34) with vertex at (-3,-2) Enter the quadratic expression in general form, ax + bx + c. Do not enter "f(x)=" f(x) =

-

What are the main operations objectives that a catering services company must achieve in order to satisfy its customers?

-

Identify one local business that uses a perpetual inventory system and another that uses a periodic system. Interview an individual in each organization who is familiar with the inventory system and...

-

Write down the binary representation of the decimal number 63.25 assuming the IEEE 754 double precision format.

-

Write down the binary representation of the decimal number 63.25 assuming it was stored using the single precision IBM format (base 16, instead of base 2, with 7 bits of exponent).

-

Write down the binary bit pattern to represent -1.5625 10 -1 assuming a format similar to that employed by the DEC PDP-8 (the left most 12 bits are the exponent stored as a twos complement number,...

-

Need help answering Part B Thank you Multiple Production Department Factory Overhead Rate Method Four Finger Appliance Company manufactures small kitchen appliances. The product line consists of...

-

Described below are six independent and unrelated situations involving accounting changes. Each change occurs during 2021 before any adjusting entries or closing entries were prepared. Assume the tax...

-

Swifty Corporation was organized on January 1, 2021. During its first year, the corporation issued 2,300 shares of $50 par value preferred stock and 140,000 shares of $10 par value common stock. At...

Study smarter with the SolutionInn App