Question: You decide to speed up the virtual memory system of Exercise 8.20 by using a translation lookaside buffer (TLB). Suppose your memory system has the

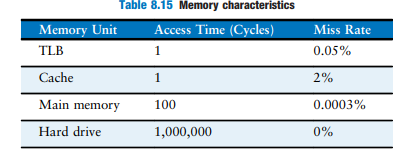

You decide to speed up the virtual memory system of Exercise 8.20 by using a translation lookaside buffer (TLB). Suppose your memory system has the characteristics shown in Table 8.15. The TLB and cache miss rates indicate how often the requested entry is not found. The main memory miss rate indicates how often page faults occur.

(a) What is the average memory access time of the virtual memory system before and after adding the TLB? Assume that the page table is always resident in physical memory and is never held in the data cache.(b) If the TLB has 64 entries, how big (in bits) is the TLB? Give numbers for data (physical page number), tag (virtual page number), and valid bits of each entry. Show your work clearly.(c) Sketch the TLB. Clearly label all fields and dimensions.(d) What size SRAM would you need to build the TLB described in part (c)? Give your answer in terms of depth ? width.

Table 8.15 Memory characteristics Memory Unit Access Time (Cycles) Miss Rate TLB 1 0.05% Cache 1 2% Main memory 100 0.0003% Hard drive 1,000,000 0%

Step by Step Solution

3.33 Rating (162 Votes )

There are 3 Steps involved in it

a From Equation 82 AMAT t cache MR cache t MM MR MM t VM However each data acc... View full answer

Get step-by-step solutions from verified subject matter experts