A 4 4 array multiplier (Figure 4-29) is to be implemented using an FPGA. (a) Partition

Question:

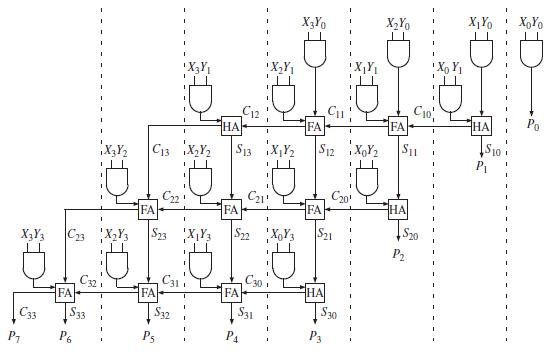

A 4 ⊗ 4 array multiplier (Figure 4-29) is to be implemented using an FPGA.

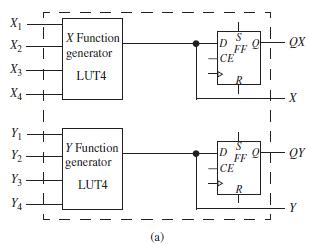

(a) Partition the logic so that it fits in a minimum number of Figure 6-1(a) logic blocks. Draw loops around each set of components that will fit in a single logic block. Determine the total number of 4-input LUTs required.

(b) Repeat part (a), except assume that carry-chain logic is available.

Figure 4-29

Figure 6.1(a)

Transcribed Image Text:

х,Y X„Y0 ХзYo X,Y0 ' Xo Y1 'X3¥1 'X,Y1 :X,ү, Си; FA C12 НА Сю; FA НА Po х,Y, S12 XQY2 | Св ху, S13 X,Y2 P1 Сдо FA C22 FA C21 FA НА Sza X,Yз Sz2 XoYз |C23 X,Y3 S21 S20 Xзуз P2 FA FA НА! FA S33 Сзв S32 S31 S30 P7 Рь Рз P4 FIGURE 4-29

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 85% (7 reviews)

a 14 cells total b 14 cells total 6 for adders and 8 f...View the full answer

Answered By

Mugdha Sisodiya

My self Mugdha Sisodiya from Chhattisgarh India. I have completed my Bachelors degree in 2015 and My Master in Commerce degree in 2016. I am having expertise in Management, Cost and Finance Accounts. Further I have completed my Chartered Accountant and working as a Professional.

Since 2012 I am providing home tutions.

3.30+

2+ Reviews

10+ Question Solved

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted:

Students also viewed these Sciences questions

-

An 8-bit right-shift register with parallel load is to be implemented using an FPGA with logic blocks as shown in Figure 6-1(a). The flip-flops are labeled X 7 X 6 X 5 X 4 X 3 X 2 X 1 X 0 . The...

-

(a) Write Verilog code that describes the following SM chart. Assume that state changes occur on the falling edge of the clock. Use two processes (b) The SM chart is to be implemented using a PLA and...

-

An n n array multiplier, as in Figure 4-29, takes 3n - 4 adder delays + 1 gate delay to calculate a product. Design an array multiplier that is faster than this for n > 4. (Instead of passing carry...

-

Assume Pelican Corp has a current Beta is 0.65 and no debt. Management wants to increase their debt load which will result in a debt/equity ratio of 0.20 Given this change, what is the new,...

-

In learning about auditing various company operations, you read about payroll as another area that is subject to fraud and errors. Choose any of the payroll functions, such as timekeeping, entering...

-

What is production planning?

-

17-10. Cules son las caractersticas de los buenos objetivos de promocin ?

-

Shortys Convenience Stores income statement for the year ended December 31, 2013, and its balance sheet as of December 31, 2013, reported the following: The business is organized as a proprietorship,...

-

In the land between gesos Cory factshem M Inde effect the convent where to see momented on the other end the be andate evento con with > A. F G 1 EX v B N M w IN 13.00 WEL Theme W > E C B N In the...

-

The Toys-R-4-U Company has developed two new toys for possible inclusion in its product line for the upcoming Christmas season. Setting up the production facilities to begin production would cost...

-

(a) Use Shannons expansion theorem to expand the following function around A and then expand each sub-function around D: Z = ABCDEF + ABCDEF + BCEF + ABCEF + ABCDE (b) Explain how the expanded...

-

(a) If logic blocks of Figure 6-1(a) are used, how many LUTs are required to build a 4-bit adder with accumulator? (b) If an FPGA with built-in carry-chain logic as shown in Figure 6-11 is used, how...

-

John sustained a severe injury during football practice and is told that he has a torn knee cartilage. Can he expect a quick, uneventful recovery? Explain your response.

-

What work trait differences are similar in chart 1 and chart 2? Provide a comment for each of the 4 generations from each chart. Which work trait differences vary from those identified in chart 1 and...

-

Given the ALU design illustrated below, without changing the circuit design, please use the ALU to perform a logic NAND operation. Find out what the control signals should be (i.e. the values of...

-

Problem #5: Using the method of joints, determine the force in each member. State whether each member is in compression or tension. If the largest force each member can support is 4kN tension and 3kN...

-

Your cultural/social background and that of your family. What language, policies/structures and customs are relevant to your own culture? How do you think your own background impacts on people from...

-

In this second Case Assignment, the assignment is going to test your understanding of how successful teams operate efficiently through teamwork. Teamwork relies upon individuals to work together to...

-

Babe Ruth was the first great slugger in baseball. His record of 60 home runs in one season held for 34 years until Roger Maris hit 61 in 1961. Mark McGwire (with the aid of steroids) set a new...

-

In the busy port of Chennai, India, the number of containers loaded onto ships during a 15-week period is as follows: 1. Develop a linear trend equation to forecast container loadings. 2. Using the...

-

Draw the mechanism for each of the following reactions: a. b. c. NaOMe CI NaOEt. Br

-

In the next chapter, we will learn a method for preparing alkynes (compounds containing C ¡ C triple bonds). In the following reaction, a dihalide (a compound with two halogen atoms) is treated...

-

Identify whether each of the following reagents would be a strong nucleophile or a weak nucleophile, and also indicate whether it would be a strong base or a weak base: a.

-

On NSE (Indian stock exchange), shares of ICICI Bank trade for 935 rupees. If the spot exchange rate is USD 0.012, what is the no-arbitrage USD price of ICICI Bank ADR? Assume that transactions costs...

-

Income Statement Balance Sheet Balance Sheet Additional Financial Information 1. Market price of Ranfield's common stock: $90.44 at December 31, 2024, and $58.35 at December 31, 2023. 2. Common...

-

There is a credit rating agency for businesses that gives out various amounts of information based on the subscription level. This company is called a. Business Credit Scoring b. Fair Issue c. Dun...

Study smarter with the SolutionInn App