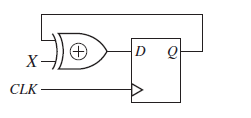

Question: In the following circuit, the XOR gate has a delay in the range of 2 to 16 ns. The D flip-flop has a propagation delay

In the following circuit, the XOR gate has a delay in the range of 2 to 16 ns. The D flip-flop has a propagation delay from clock to Q in the range 12 to 24 ns. The setup time is 8 ns, and the hold time is 4 ns.

(a) What is the minimum clock period for proper operation of the circuit?

(b) What are the earliest and latest times after the rising clock edge at which X is allowed to change and still have proper synchronous operation? (Assume minimum clock period from (a).)

X - CLK -

Step by Step Solution

3.45 Rating (161 Votes )

There are 3 Steps involved in it

a 16 ns 24 ns 8 ns 48 ns to satisfy setup time hold time is not a prob... View full answer

Get step-by-step solutions from verified subject matter experts