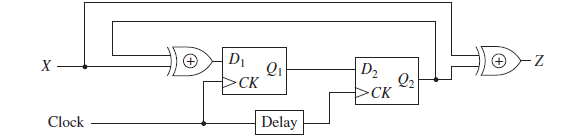

Question: In the following circuit, the XOR gate has a delay in the range of 2 to 16 ns. The D flip-flop has a propagation delay

In the following circuit, the XOR gate has a delay in the range of 2 to 16 ns. The D flip-flop has a propagation delay from clock to Q in the range 12 to 24 ns. The setup

time is 8 ns, and the hold time is 4 ns.

(a) Assume delay = 0 ns and compute the maximum frequency at which this circuit can be safely clocked.

(b) Assume delay = 5 ns and compute the maximum frequency at which this circuit can be safely clocked.

(c) Assume delay = €“5 ns (i.e., the first flip gets the clock delayed 5 ns as compared with the second flip-flop) and compute the maximum frequency at which this circuit can be safely clocked.

(d) Assume delay = 0 ns and compute the earliest time and latest times after or before the rising clock edge that X is allowed to change and still have proper synchronous operation?

(e) Assume delay = 5 ns and compute the earliest time and latest times after or before the rising clock edge at which X is allowed to change and still have proper synchronous operation?

(f) Assume delay = €“5 ns and compute the earliest time and latest times after or before the rising clock edge at which X is allowed to change and still have proper synchronous operation?

D1 Qi >CK D2 Q2 >CK Clock Delay

Step by Step Solution

3.38 Rating (173 Votes )

There are 3 Steps involved in it

a The maximum delay path of this circuit starts at flipflop 2 and ends at flipflop 1 ... View full answer

Get step-by-step solutions from verified subject matter experts