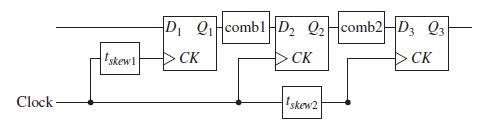

Consider the following circuit where the combinational circuit is represented by COMB and clock skew is represented

Question:

Given the following parameters:

FF setup time = 20 ns

FF hold time = 10 ns

FF propagation delay = 5 to 10 ns

Tcomb 1 = 5 ns to 7 ns

Tcomb 2 = 6 ns to 11 ns

(a) What is the minimum clock period with tskew1 = tskew2 = 0?

(b) Now set Tcomb1 = 1 to 4 ns. Is there a setup time violation for the middle flip-flop? If no, what is the setup time margin?

(c) Now set Tcomb1 = 1 to 4 ns. Is there a hold-time violation for the middle flip-flop? If no, what is the hold-time margin?

(d) What are the minimum values of tskew1 and tskew2 that will fix the violations?

(e) What is the minimum clock period after violations have been fixed?

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: