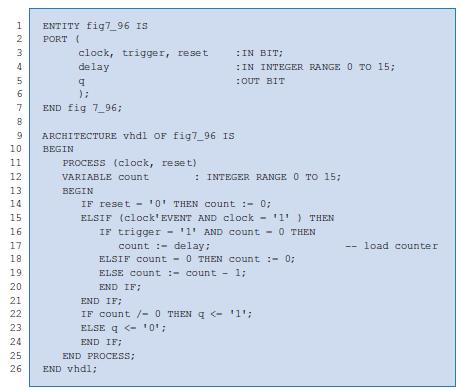

Modify the nonretriggerable, level-sensitive, one-shot design example from either Figure 7-95 (AHDL) or Figure 7-96 (VHDL) so

Question:

Modify the nonretriggerable, level-sensitive, one-shot design example from either Figure 7-95 (AHDL) or Figure 7-96 (VHDL) so that the one-shot is retriggerable but still level-sensitive. Simulate the design.

Figure 7-95

![12345 6 7 8 9 SUBDESIGN fig7_95 ( ) clock, trigger, reset delay [3..0] q VARIABLE count [3..0] BEGIN 10 11 12](https://dsd5zvtm8ll6.cloudfront.net/images/question_images/1699/9/6/3/7886553638c8cef91699963788806.jpg)

Figure 7-96

Transcribed Image Text:

12345 6 7 8 9 SUBDESIGN fig7_95 ( ) clock, trigger, reset delay [3..0] q VARIABLE count [3..0] BEGIN 10 11 12 13. 14 15 16 17 18 END; : DFF; count[].clk - clock; count[].clrn - reset; IF trigger & count [].qb"0000" THEN count[].d delay []; : INPUT; : INPUT; : OUTPUT: ELSIF count[].qB"0000" THEN count[].d - B"0000"; ELSE count[].d count[].q- 1; END IF; q count[].q - B"0000"; -- make output pulse

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 100% (3 reviews)

Answered By

Utsab mitra

I have the expertise to deliver these subjects to college and higher-level students. The services would involve only solving assignments, homework help, and others.

I have experience in delivering these subjects for the last 6 years on a freelancing basis in different companies around the globe. I am CMA certified and CGMA UK. I have professional experience of 18 years in the industry involved in the manufacturing company and IT implementation experience of over 12 years.

I have delivered this help to students effortlessly, which is essential to give the students a good grade in their studies.

3.50+

2+ Reviews

10+ Question Solved

Related Book For

Digital Systems Principles And Application

ISBN: 9780134220130

12th Edition

Authors: Ronald Tocci, Neal Widmer, Gregory Moss

Question Posted:

Students also viewed these Computer science questions

-

Planning is one of the most important management functions in any business. A front office managers first step in planning should involve determine the departments goals. Planning also includes...

-

Project the 2 4-1 IV design in Example 8-1 into two replicates of a 2 2 design in the factors A and B. Analyze the data and thaw conclusions. Example 8-1: Consider the filtration rate experiment in...

-

Managing Scope Changes Case Study Scope changes on a project can occur regardless of how well the project is planned or executed. Scope changes can be the result of something that was omitted during...

-

If a natural disaster, such as the 2010 drought in Russia, hits food production, use supply and demand analysis to figure out how this affects consumers and producers. Does everyone lose or are some...

-

A company that we call DC is a Fortune 100 diversified conglomerate with operations in many industries around the world. Top management focuses on the annual earnings in evaluating the performance of...

-

A simplified representation of the temperature dynamics of two adjacent masses is shown in Figure. The mass with capacitance C2 is perfectly insulated on all sides except one, which has a convective...

-

1. Is the sequence OXXXOXXXOXXOOOXOOXXOO random? a. Probably random b. Probably not random

-

Briefly describe some of the similarities and differences between U.S. GAAP and iGAAP with respect to the accounting for intangible assets .

-

Nike is looking to produce on of 3 different shoe options. It is your job to decide which shoe to manufacture. The shoe's information is listed below. Please use excel and show equations Nike Zoom...

-

Suppose Ann is working on a project with John. Both must decide whether to put into a decent amount of effort into the project. Since Ann is the leader of the project, her contribution determines...

-

For each of the following statements, indicate the type(s) of counter being described. (a) Each FF is clocked at the same time. (b) Each FF divides the frequency at its CLK input by 2. (c) The...

-

Sometimes a digital application may need a ring counter that recirculates a single zero instead of a single one. The ring counter would then have an active-LOW output instead of an active-HIGH....

-

What was the value of the Canadian dollar in terms of U.S. dollars in June 2011 and June 2012? Did the Canadian dollar appreciate or depreciate against the U.S. dollar over the year June 2011 to June...

-

6. [-/2.94 Points] DETAILS WANEFMAC8 12.2.037.EP. MY NOTES ASK YOUR TEACHER 1,500 The demand equation for your company's virtual reality video headsets is p = where q is the total number of headsets...

-

V W R + |, V W R R3 w V3 V In the above circuit diagram, if V=12V, R =42, R2=62, R3=12.2. What would be the value of current I? (Hint: use Kirchhoff's law) 2 0.5A 1.5A 1A 2A

-

A company produces a single product that has the following standard costs: Materials Labor 5 pieces at P4 per piece P20 3 hours at P10 per hour 30 Variable Overhead 3 hours at P15 per hour 45 Fixed...

-

Use the graph to answer each part. K (a) List all the even vertices and all the odd vertices. Click on "None" as needed. List of the even vertices: List of the odd vertices: (b) List all vertices...

-

My software development company has the databases, tools, and staff to design up to 24 programs per week with an effective capacity of 17 programs per week. What is its efficiency if it designs an...

-

In the design of an automobile radiator, an engineer has a choice of using either a brass-copper alloy casting or a plastic molding. Either material provides the same service. However, the...

-

Walker, Inc., is an all-equity firm. The cost of the company's equity is currently 11.4 percent and the risk-free.rate is 3.3 percent. The company is currently considering a project that will cost...

-

In the air over a particular region at an altitude of 500 m above the ground the electric field is 120 N/C directed downward. At 600 m above the ground the electric field is 100 N/C downward. What is...

-

A point charge Q = 5.00 %C is located at the center of a cube of edge L = 0.100 m. In addition, six other identical point charges having q = -1.00 %C are positioned symmetrically around Q as shown in...

-

A positive point charge Q is located at the center of a cube of edge L. In addition, six other identical negative point charges q are positioned symmetrically around Q as shown in Figure P24.17....

-

Your firm has the opportunity to repurpose one of its facilities and use it to invest in a new product that would change the profits of your firm for the next four years as follows: Year Before After...

-

The Clark County Sheriff's Department schedules police officers for 8-hour shifts. The beginning times for the shifts are 8:00 a.m., noon, 4:00 p.m., 8:00 p.m., midnight, and 4:00 a.m. An officer...

-

Selected comparative financial statements of Korbin Company follow: KORGIN COMPANY Comparative Income Statements For Years Ended December 31, 2014, 2013, and 2012 2014 2013 2012 Sales $390,872...

Study smarter with the SolutionInn App