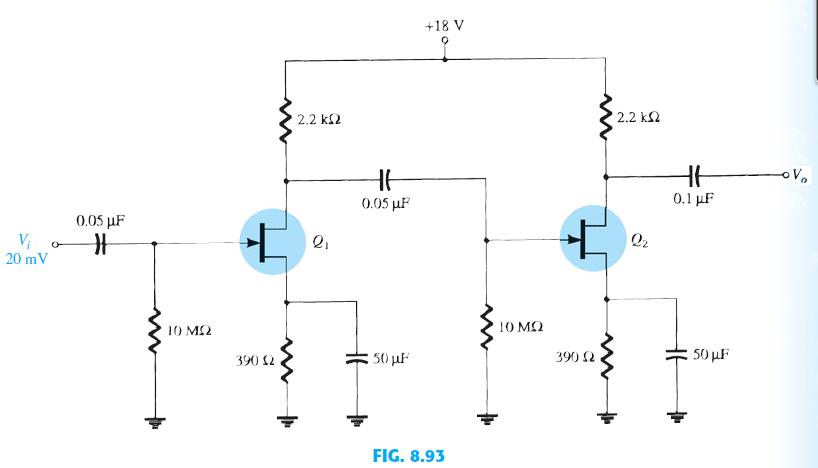

Use the Design Center to draw a schematic circuit of the cascade JFET amplifier as in Fig.8.93.

Question:

Use the Design Center to draw a schematic circuit of the cascade JFET amplifier as in Fig.8.93. Set the JFET parameters for IDSS = 12 mA and VP = 3V, and have the analysis determine the dc bias.

Fig.8.93

Transcribed Image Text:

+18 V 2.2 k2 2.2 k 0.05 µF 0.1 µF 0.05 µF 20 mV 10 M2 10 M2 390 2. 50 µF 50 µF 390 2 FIG. 8.93

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 75% (16 reviews)

Use the Design Center to draw a schematic circuit of the cascade ...View the full answer

Answered By

Labindao Antoque

I graduated in 2018 with a Bachelor of Science degree in Psychology from Dalubhasaan ng Lungsod ng San Pablo. I tutored students in classes and out of classes. I use a variety of strategies to tutor students that include: lecture, discussions about the subject matter, problem solving examples using the principles of the subject matter being discussed in class , homework assignments that are directed towards reinforcing what we learn in class , and detailed practice problems help students to master a concept. I also do thorough research on Internet resources or textbooks so that I know what students need to learn in order to master what is being taught in class .

0.00

0 Reviews

10+ Question Solved

Related Book For

Electronic Devices And Circuit Theory

ISBN: 9781292025636

11th Edition

Authors: Robert Boylestad, Louis Nashelsky

Question Posted:

Students also viewed these Engineering questions

-

Use the Design Center to draw a schematic circuit for a cascade JFET amplifier as shown in Fig. 8.93 . Set the analysis to calculate the ac output voltage V o for I DSS = 12 mA and V P = 3V. Fig....

-

Given IDSS = 12 mA and VP = 4 V, Draw the Drain characteristics for a p-JFET.

-

Fig. 18.43 shows a schematic circuit of an instrument called a potentiometer, which is a device for determining very accurate emf values of power supplies. It consists of three batteries, an ammeter,...

-

A posthole digger (the digger) is an agricultural implement manufactured by Alamo/SMC Corporation (SMC) designed, as its name implies, to dig holes in the ground for posts. The digger is...

-

State the law of supply. Why is price directly related to quantity supplied?

-

Kaler Company has sales of $1,210,000, cost of goods sold of $735,000, other operating expenses of $148,000, average invested assets of $3,400,000, and a hurdle rate of 12 percent. Required: 1....

-

SAT essayis longer better? Following the debut of the new SAT Writing test in March 2005, Dr. Les Perelman from the Massachusetts Institute of Technology recorded the number of words and score for...

-

Inventory Costing MethodsPeriodic System Following is an inventory acquisition schedule for Weaver Corp. for 2010: During the year, Weaver sold 12,500 units at $12 each. All expenses except cost of...

-

[10:34 p.m., 2021-10-10] Muskaan Roomie: Suppose that you are the CEO of a company that is about to market an affordable, low-emissions car. Mass production of this car could potentially lead to the...

-

Compare the plans developed in Exercise 7.33 in terms of average fraction inspected and their operating-characteristic curves. Which plan would you prefer if ? Exercise 7.33 Suppose that CSP-1 is...

-

Determine: a. 20 log 10 using Eq. (9.6) and compare with 20 log 10 14. b. 10 log 10 using Eq. (9.7) and compare with 10log 10 4 10 -3 . c. log 10 (40)(0.2) using Eq. (9.8) and compare with log10 8...

-

Using Multisim, determine the voltage gain for the network o Fig. 8.77. Fig. 8.77 +15 V 3.3 k2 Ipss = 8 mA Vp=-2.8 V ra= 40 k2 Zo 1.5 k2 FIG. 8.77

-

Multiply 1,234,567 9,999,999 a. Using a calculator b. Using patterns

-

A company which manufactures microwaves advertises that 90% of their microwaves are flawless, requiring no adjustments. Their quality control department tests this percentage on a regular basis. On...

-

A new retail store is being planned for a site that contains 40 ft of soft clay (c 0.075 ft2/day, y = 100 pcf). The clay layer is overlain by 15 ft of sand (y = 112 pcf) and is underlain by dense...

-

Perez Bags (PB) is a designer of high-quality backpacks and purses. Each design is made in small batches. Each spring, PB comes out with new designs for the backpack and for the purse. The company...

-

Find a recent (within the last 12 months) article or economic blog related to price fixing, provide an executive summary of the information. Include an APA reference and/or link. How does the fact...

-

A rectangular block of a material with a modulus of rigidity G=90 ksi is bonded to two rigid horizontal plates. The lower plate is fixed, while the upper plate is subjected to a horizontal force P....

-

For an SKU, the standard deviation of demand during the lead time is 150 units, the annual demand is 10,000 units, and the order quantity is 750 units. Management says it will tolerate only one...

-

Beginning with a country that has a trade deficit, demonstrate graphically what will happen to a countrys potential output with globalization if that countrys costs of production fall. Explain your...

-

A solution of NaOH was standardized by titration of a known quantity of the primary standard, potassium hydrogen phthalate The NaOH was then used to find the concentration of an unknown solution of H...

-

Write the names and abbreviations for each of the prefixes from 10 -24 to 10 24 . Which abbreviations are capitalized?

-

What is the formal concentration (expressed as mol/L = M) of NaCl when 32.0 g are dissolved in water and diluted to 0.500 L?

-

Just work out the assignment on your own sheet, you dont need the excel worksheet. Classic Coffee Company Best friends, Nathan and Cody, decided to start their own business which would bring great...

-

Financial information related to the proprietorship of Ebony Interiors for February and March 2019 is as follows: February 29, 2019 March 31, 2019 Accounts payable $310,000 $400,000 Accounts...

-

(b) The directors of Maureen Company are considering two mutually exclusive investment projects. Both projects concern the purchase of a new plant. The following data are available for each project...

Study smarter with the SolutionInn App