Question: 22. You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set-associative cache, and a page table for a process P. Assume

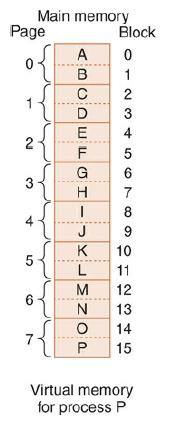

22. You have a byte-addressable virtual memory system with a two-entry TLB, a 2-way set-associative cache, and a page table for a process P. Assume cache blocks of 8 bytes and page size of 16 bytes.

In the system below, main memory is divided into blocks, where each block is represented by a letter. Two blocks equal one frame.

Given the system state as depicted above, answer the following questions:

1.

a) How many bits are in a virtual address for process P?

Explain.

2.

b) How many bits are in a physical address? Explain.

3.

c) Show the address format for virtual address 0x12 (specify field name and size) that would be used by the system to translate to a physical address and then translate this virtual address into the corresponding physical address. (Hint:

Convert the address to its binary equivalent and divide it into the appropriate fields.) Explain how these fields are used to translate to the corresponding physical address.

4.

d) Given virtual address 0x06 converts to physical address 0x36. Show the format for a physical address (specify the field names and sizes) that is used to determine the cache location for this address. Explain how to use this format to determine where physical address 0x36 would be located in cache. (Hint: Convert 0x36 to binary and divide it into the appropriate fields.)

5.

e) Given virtual address 0x19 is located on virtual page 1, offset 9. Indicate exactly how this address would be translated to its corresponding physical address and how the data would be accessed. Include in your explanation how the TLB, the page table, cache, and memory are used.

Page Frame 0 3 4 1 TLB TAG DATA TAG DATA Set 0 00 01 Set 1 00 D 10 H Cache 0 1 234569 7 Frame Valid 30 Frame - 2 1 - - 1 1 0 1 1 0 0 0 Page table Block 0 1 234561 CDIGHAB L 2 3 7

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts