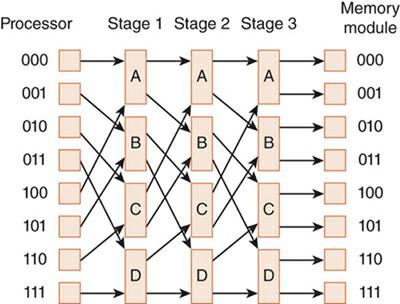

Given the following Omega network, which allows eight CPUs (P0 through P7) to access eight memory modules

Question:

Given the following Omega network, which allows eight CPUs

(P0 through P7) to access eight memory modules (M0 through M7):

1.

a) Show how the following connections through the network are achieved (explain how each switch must be set). Refer to the switches as 1A, 2B, etc.:

1. i) P0 → M2 2. ii) P4 → M4 3. iii) P6 → M3 2.

b) Can these connections occur simultaneously, or do they conflict? Explain.

3.

c) List a processor-to-memory access that conflicts (is blocked) by the access P0 → M2 and is not listed in Part (a).

4.

d) List a processor-to-memory access that is not blocked by the access P0 → M2 and is not listed in Part (a).

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Essentials Of Computer Organization And Architecture

ISBN: 9781284123036

5th Edition

Authors: Linda Null, Julia Lobur

Question Posted: