Question: Design a ternary full-adder circuit, using the approach described in Problem 3.25. Data From Problem 3.25 In a ternary number system there are three digits:

Design a ternary full-adder circuit, using the approach described in Problem 3.25.

Data From Problem 3.25

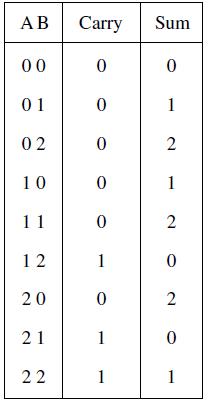

In a ternary number system there are three digits: 0, 1, and 2. Figure P3.3 defines a ternary half-adder. Design a circuit that implements this half-adder using binary-encoded signals, such that two bits are used for each ternary digit. Let A = a1a0, B = b1b0, and Sum = s1s0; Carry is just a binary signal. Use the following encoding: 00 = (0)3, 01 = (1)3, and 10 = (2)3. Minimize the cost of the circuit.

AB Carry 00 01 02 10 11 12 20 21 22 0 0 0 0 0 1 0 1 1 Sum 0 1 2 1 2 0 2 0 1

Step by Step Solution

3.42 Rating (155 Votes )

There are 3 Steps involved in it

Full adder takes three inputs namely A B and C in Where ... View full answer

Get step-by-step solutions from verified subject matter experts