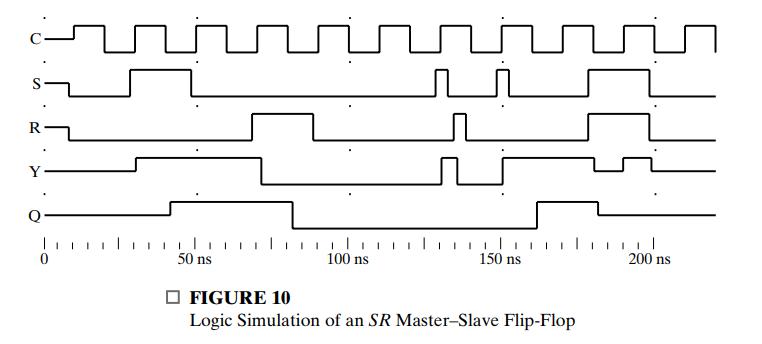

Obtain a timing diagram similar to Figure 10 for a positive-edge-triggered (J K) flip-flop during four clock

Question:

Obtain a timing diagram similar to Figure 10 for a positive-edge-triggered \(J K\) flip-flop during four clock pulses. Show the timing signals for \(C, J, K, Y\), and \(Q\). Assume that initially the output \(Q\) is equal to 1 , with \(J=0\) and \(K=1\) for the first pulse. Then, for successive pulses, \(J\) goes to 1 , followed by \(K\) going to 0 and then \(J\) going back to 0 . Assume that each input changes near the negative edge of the pulse.

Data From Figure 10

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Logic And Computer Design Fundamentals

ISBN: 9781292024684

4th International Edition

Authors: M. Morris Mano, Charles Kime

Question Posted: