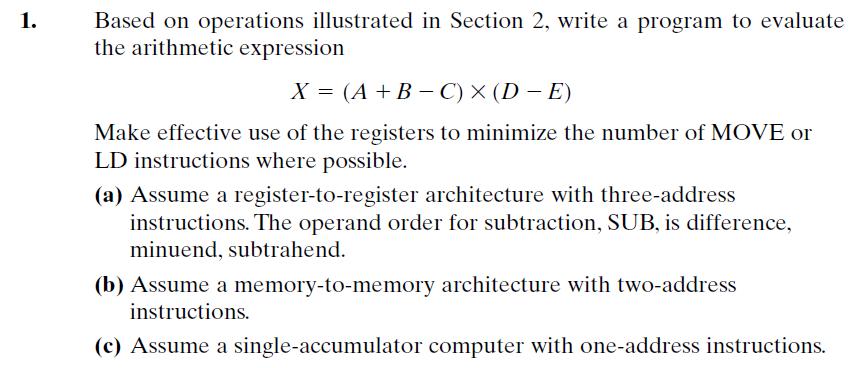

Logic And Computer Design Fundamentals 5th Edition M. Morris Mano, Charles Kime, Tom Martin - Solutions

Unlock the potential of your studies with our comprehensive guide to "Logic and Computer Design Fundamentals, 5th Edition" by M. Morris Mano, Charles Kime, and Tom Martin. Explore a treasure trove of online resources, including a detailed answers key and complete solution manual available in PDF format. Dive into solved problems and step-by-step answers that cover every chapter, providing a robust test bank for your learning needs. Access instructor manuals and textbook solutions for free download, ensuring you have the tools to succeed. Discover an unparalleled collection of questions and answers designed to elevate your understanding and mastery of the subject.

![]()

![]() New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

New Semester Started

Get 50% OFF

Study Help!

--h --m --s

Claim Now

![]()

![]()