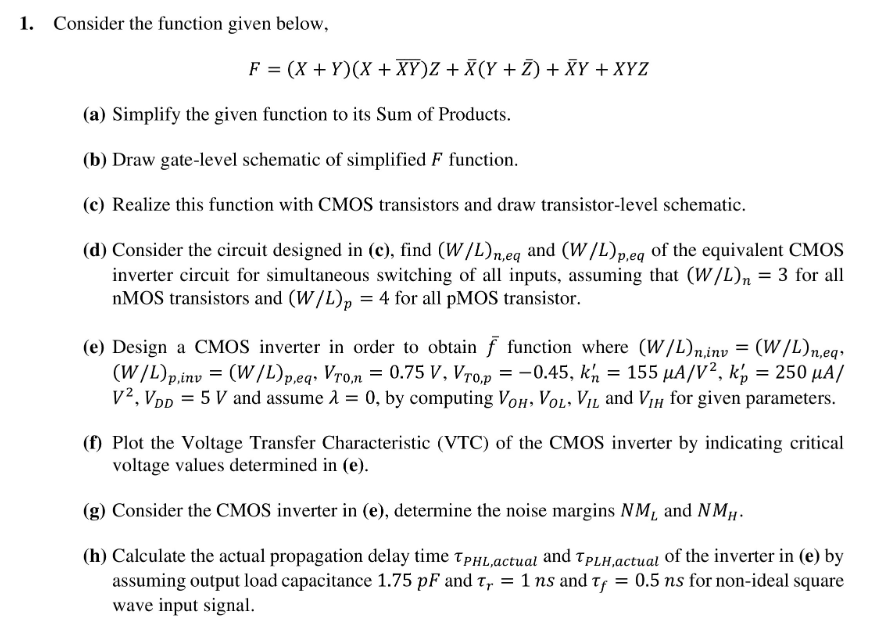

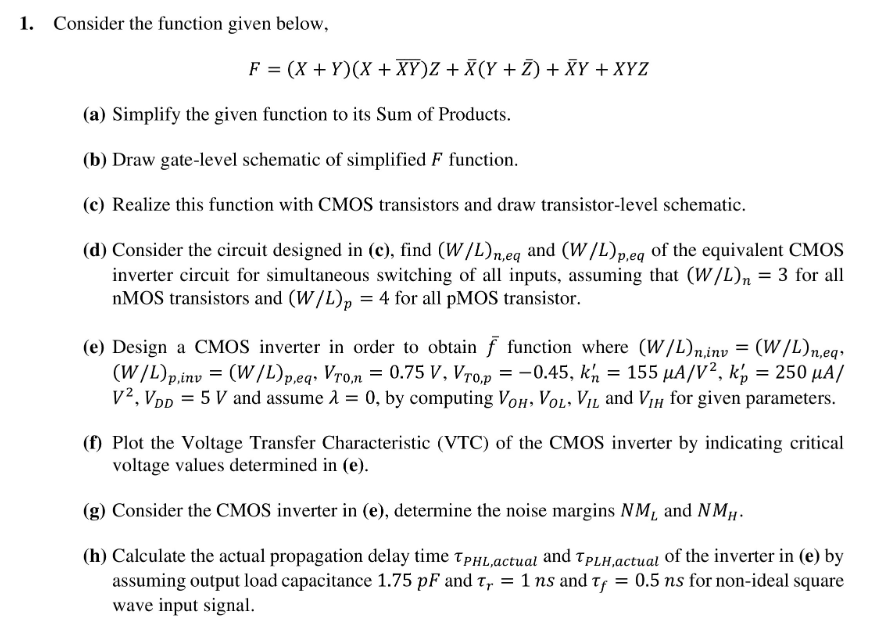

1. Consider the function given below, F = (X+Y)(X + XY)Z + X(Y + 7) + XY + XYZ (a) Simplify the given function to its Sum of Products. (b) Draw gate-level schematic of simplified F function. (c) Realize this function with CMOS transistors and draw transistor-level schematic. (d) Consider the circuit designed in (e), find (W/L) n,eq and (W/L)p,eg of the equivalent CMOS inverter circuit for simultaneous switching of all inputs, assuming that (W/L)n = 3 for all nMOS transistors and (W/L) p = 4 for all pMOS transistor. (e) Design a CMOS inverter in order to obtain f function where (W/L)n,iny = (W/L)n,eq, (W/L)p,inv = (W/L)p,q, Vro,n = 0.75 V, VTO,p = -0.45, kn = 155 uA/V2, k'= 250 uA/ V2, Vpp = 5 V and assume 1 = 0, by computing Voh, Vol, Vic and Vi for given parameters. (f) Plot the Voltage Transfer Characteristic (VTC) of the CMOS inverter by indicating critical voltage values determined in (e). (g) Consider the CMOS inverter in (e), determine the noise margins NM, and NMH. (h) Calculate the actual propagation delay time Tphl,actual and TPLH,actual of the inverter in (e) by assuming output load capacitance 1.75 pF and Tr = 1 ns and t; = 0.5 ns for non-ideal square wave input signal. 1. Consider the function given below, F = (X+Y)(X + XY)Z + X(Y + 7) + XY + XYZ (a) Simplify the given function to its Sum of Products. (b) Draw gate-level schematic of simplified F function. (c) Realize this function with CMOS transistors and draw transistor-level schematic. (d) Consider the circuit designed in (e), find (W/L) n,eq and (W/L)p,eg of the equivalent CMOS inverter circuit for simultaneous switching of all inputs, assuming that (W/L)n = 3 for all nMOS transistors and (W/L) p = 4 for all pMOS transistor. (e) Design a CMOS inverter in order to obtain f function where (W/L)n,iny = (W/L)n,eq, (W/L)p,inv = (W/L)p,q, Vro,n = 0.75 V, VTO,p = -0.45, kn = 155 uA/V2, k'= 250 uA/ V2, Vpp = 5 V and assume 1 = 0, by computing Voh, Vol, Vic and Vi for given parameters. (f) Plot the Voltage Transfer Characteristic (VTC) of the CMOS inverter by indicating critical voltage values determined in (e). (g) Consider the CMOS inverter in (e), determine the noise margins NM, and NMH. (h) Calculate the actual propagation delay time Tphl,actual and TPLH,actual of the inverter in (e) by assuming output load capacitance 1.75 pF and Tr = 1 ns and t; = 0.5 ns for non-ideal square wave input signal