Question

1) Consider the instruction seq, which has the format: seq $rd, $rs, $rt. a. The instruction sets $rd to 1 if and only if $rs

1) Consider the instruction seq, which has the format: seq $rd, $rs, $rt.

a. The instruction sets $rd to 1 if and only if $rs == $rt. Otherwise it sets $rd to 0. i.

i. Provide an informal RTL (register transfer language) describing the instruction semantics

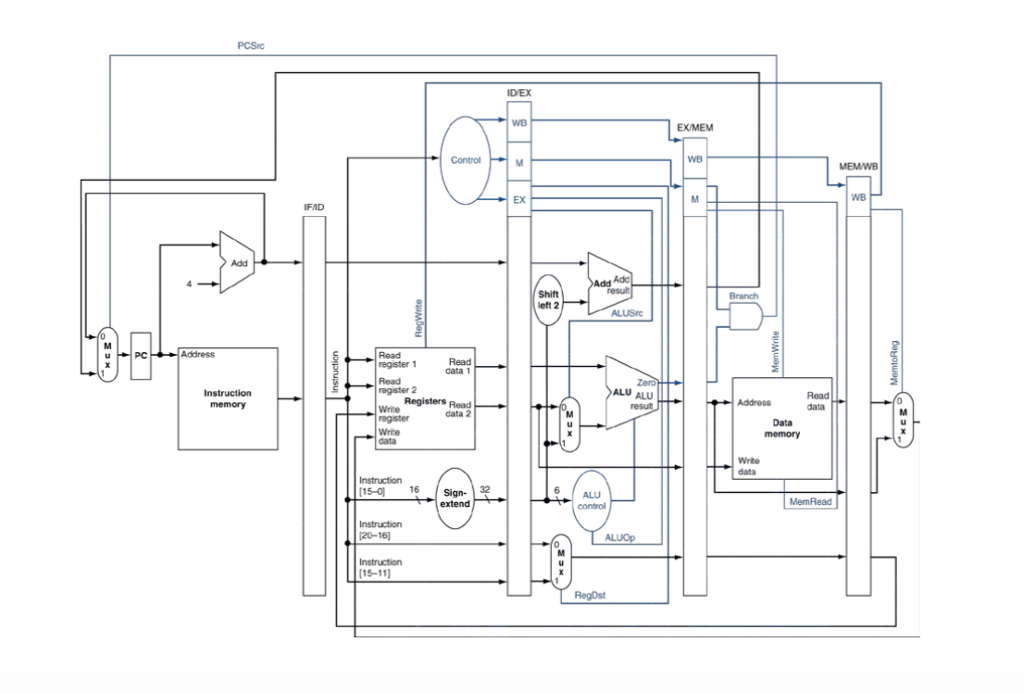

ii. Explain the way that the instruction is mapped into slide 4-66 from the book by Patterson (below).

2) Consider the instruction sovi, which has the format: sovi $rt, $rs, constant.

a. The instruction sets $rt to 1 if and only if the overflow flag is set. Otherwise it sets $rt to 0. Next, in any case the instruction resets the overflow flag to 0.

i. Provide an informal RTL (register transfer language) describing the instruction semantics

ii. Explain the way that the instruction is mapped into slide 4-66 from the book by Patterson (below).

3) Consider the instruction swi which has the format: swi $rd, $rt($rs). The instruction stores the contents of the register $rd into the memory address pointed to by $rs + $rt.

i. Provide an informal RTL (register transfer language) describing the instruction semantics

ii. Explain the way that the instruction is mapped into slide 4-66 from the book by Patterson (below).

4) Consider the instruction ballt, which has the format: ballt $rt, $rs, func. The instruction calls the function func if and only if $rs

i. Provide an informal RTL (register transfer language) describing the instruction semantics

ii. Explain the way that the instruction is mapped into slide 4-66 from the book by Patterson (below).

5) Consider the instruction beq $0, $0 out. This instruction might be considered as an exception with respect to branch prediction since it is an unconditional change of flow.

a. What type of hardware mechanism should be used with respect to branch prediction in this case?

b. How should the compiler treat this instruction if no brunch prediction is available in the hardware.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started