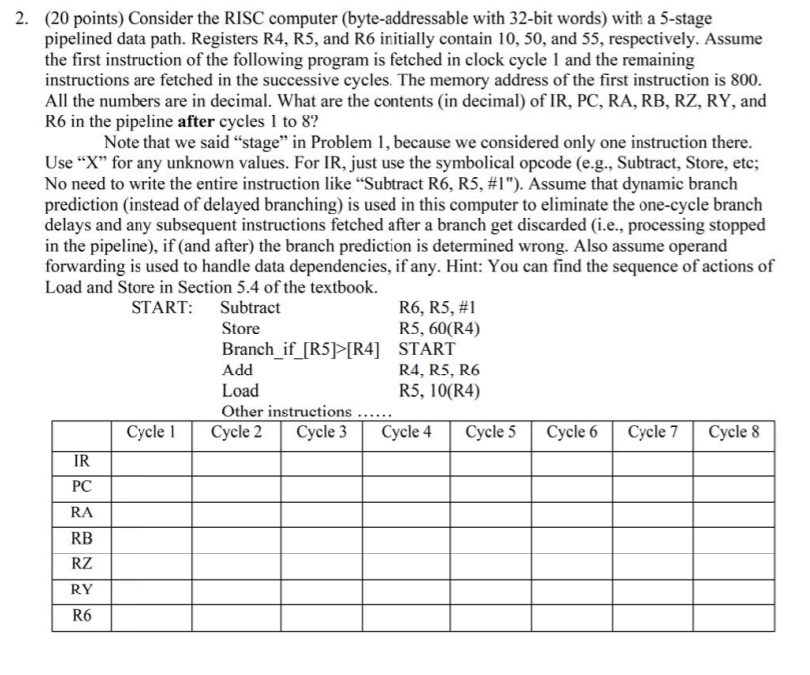

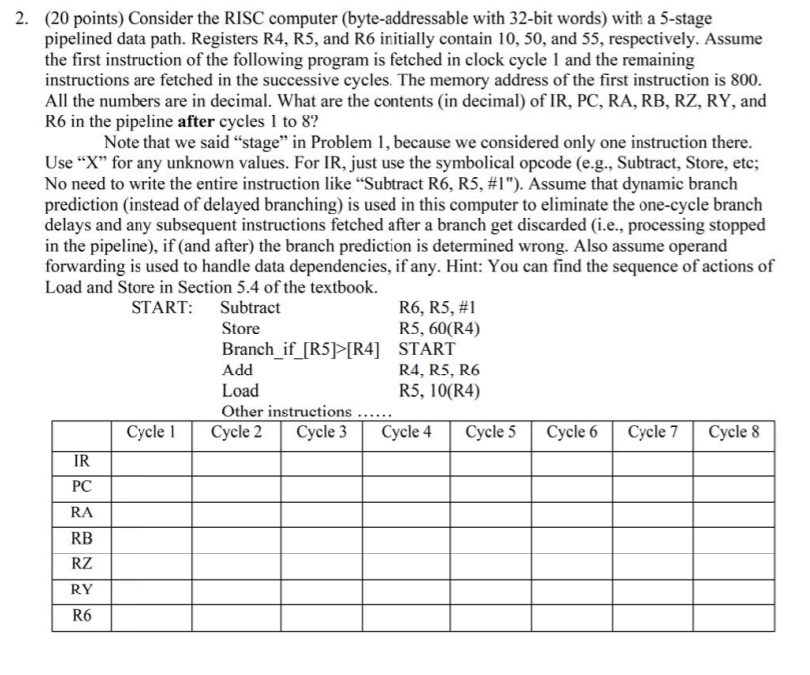

2. (20 points) Consider the RISC computer (byte-addressable with 32-bit words) with a 5-stage pipelined data path. Registers R4, R5, and R6 initially contain 10, 50, and 55, respectively. Assume the first instruction of the following program is fetched in clock cycle 1 and the remaining instructions are fetched in the successive cycles. The memory address of the first instruction is 800 All the numbers are in decimal. What are the contents (in decimal) of IR, PC, RA, RB, RZ, RY, and R6 in the pipeline after cycles 1 to 8? Note that we said "stage" in Problem 1, because we considered only one instruction there. Use X for any unknown values. For IR, just use the symbolical opcode (e.g., Subtract, Store, etc; No need to write the entire instruction like "Subtract R6, R5, #1"). Assume that dynamic branch prediction (instead of delayed branching) is used in this computer to eliminate the one-cycle branch delays and any subsequent instructions fetched after a branch get discarded (i.e., processing stopped in the pipeline), if (and after) the branch prediction is determined wrong. Also assume operand forwarding is used to handle data dependencies, if any. Hint: You can find the sequence of actions of Load and Store in Section 5.4 of the textbook. START: Subtract R6, R5, #1 R5, 60(R4) Store Branch if R51 R4] START Add R4, R5, R6 R5, 10(R4) oa Other instructions Cycle Cycle 2Cycle 3 Cycle 4Cycle 5 Cycle 6 Cycle 7Cycle 8 IR PC RA RB RZ RY R6 2. (20 points) Consider the RISC computer (byte-addressable with 32-bit words) with a 5-stage pipelined data path. Registers R4, R5, and R6 initially contain 10, 50, and 55, respectively. Assume the first instruction of the following program is fetched in clock cycle 1 and the remaining instructions are fetched in the successive cycles. The memory address of the first instruction is 800 All the numbers are in decimal. What are the contents (in decimal) of IR, PC, RA, RB, RZ, RY, and R6 in the pipeline after cycles 1 to 8? Note that we said "stage" in Problem 1, because we considered only one instruction there. Use X for any unknown values. For IR, just use the symbolical opcode (e.g., Subtract, Store, etc; No need to write the entire instruction like "Subtract R6, R5, #1"). Assume that dynamic branch prediction (instead of delayed branching) is used in this computer to eliminate the one-cycle branch delays and any subsequent instructions fetched after a branch get discarded (i.e., processing stopped in the pipeline), if (and after) the branch prediction is determined wrong. Also assume operand forwarding is used to handle data dependencies, if any. Hint: You can find the sequence of actions of Load and Store in Section 5.4 of the textbook. START: Subtract R6, R5, #1 R5, 60(R4) Store Branch if R51 R4] START Add R4, R5, R6 R5, 10(R4) oa Other instructions Cycle Cycle 2Cycle 3 Cycle 4Cycle 5 Cycle 6 Cycle 7Cycle 8 IR PC RA RB RZ RY R6