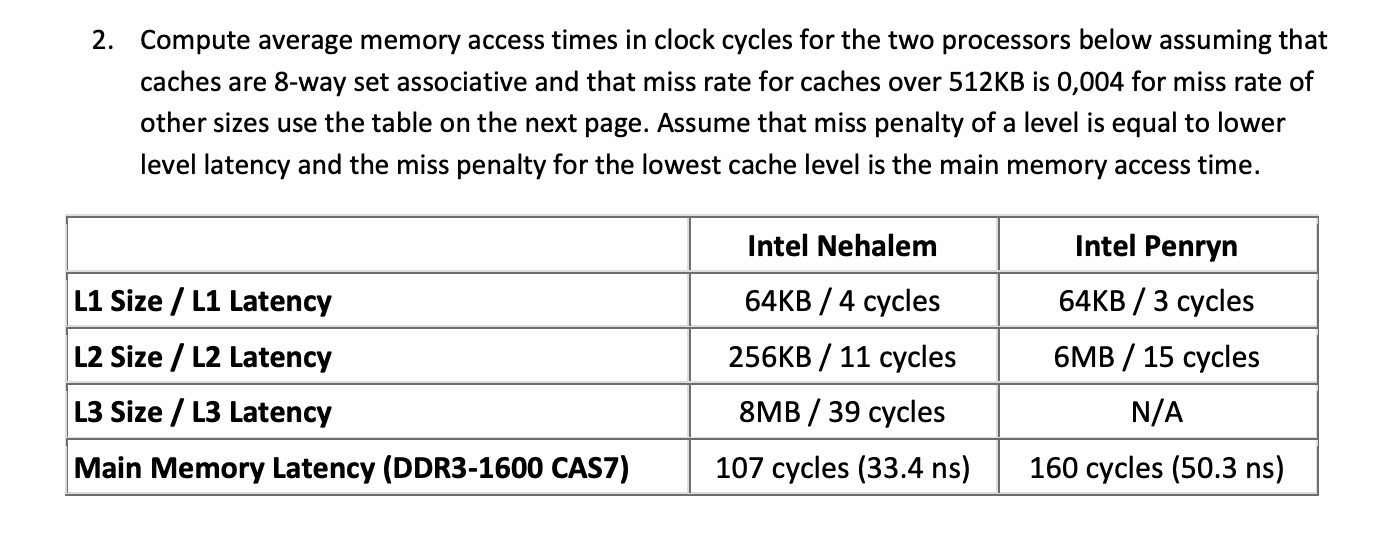

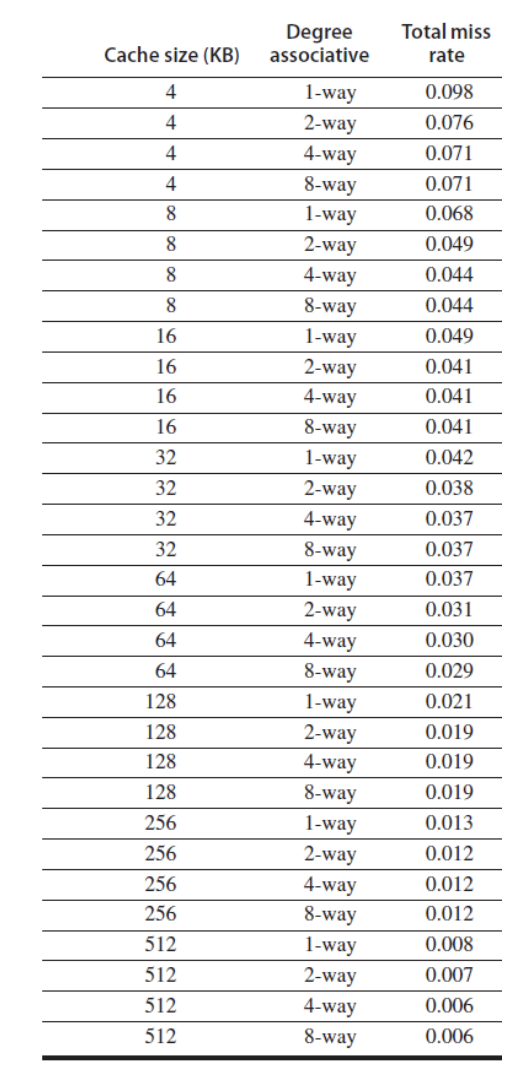

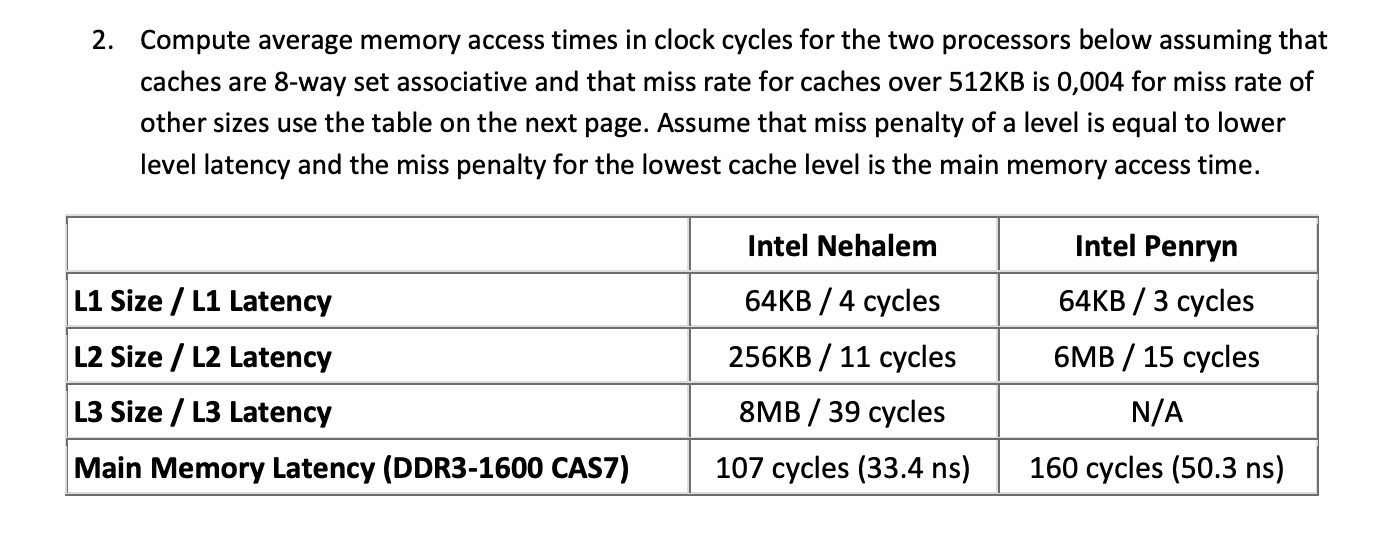

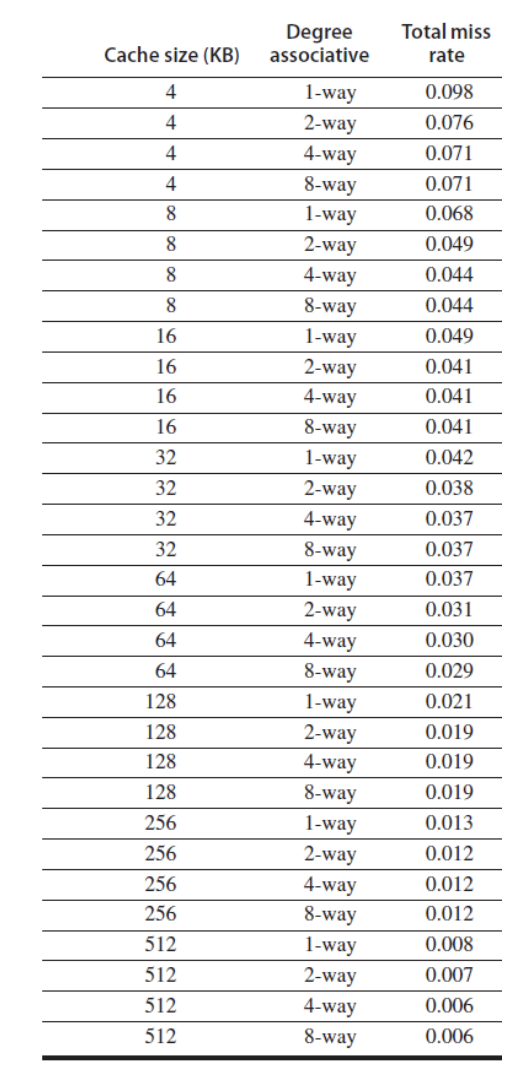

2. Compute average memory access times in clock cycles for the two processors below assuming that caches are 8-way set associative and that miss rate for caches over 512KB is 0,004 for miss rate of other sizes use the table on the next page. Assume that miss penalty of a level is equal to lower level latency and the miss penalty for the lowest cache level is the main memory access time. Intel Nehalem Intel Penryn 64KB / 3 cycles L1 Size / L1 Latency 64KB / 4 cycles 256KB / 11 cycles L2 Size / L2 Latency L3 Size / L3 Latency 8MB / 39 cycles 6MB / 15 cycles N/A 160 cycles (50.3 ns) Main Memory Latency (DDR3-1600 CAS7) 107 cycles (33.4 ns) Cache size (KB) Degree associative Total miss rate 4 4 4 0.098 0.076 0.071 0.071 0.068 4 8 8 0.049 8 8 16 16 16 16 32 32 32 32 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 64 64 64 0.044 0.044 0.049 0.041 0.041 0.041 0.042 0.038 0.037 0.037 0.037 0.031 0.030 0.029 0.021 0.019 0.019 0.019 0.013 0.012 0.012 0.012 0.008 0.007 0.006 64 128 128 128 128 256 256 256 256 512 512 512 512 0.006 2. Compute average memory access times in clock cycles for the two processors below assuming that caches are 8-way set associative and that miss rate for caches over 512KB is 0,004 for miss rate of other sizes use the table on the next page. Assume that miss penalty of a level is equal to lower level latency and the miss penalty for the lowest cache level is the main memory access time. Intel Nehalem Intel Penryn 64KB / 3 cycles L1 Size / L1 Latency 64KB / 4 cycles 256KB / 11 cycles L2 Size / L2 Latency L3 Size / L3 Latency 8MB / 39 cycles 6MB / 15 cycles N/A 160 cycles (50.3 ns) Main Memory Latency (DDR3-1600 CAS7) 107 cycles (33.4 ns) Cache size (KB) Degree associative Total miss rate 4 4 4 0.098 0.076 0.071 0.071 0.068 4 8 8 0.049 8 8 16 16 16 16 32 32 32 32 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 1-way 2-way 4-way 8-way 64 64 64 0.044 0.044 0.049 0.041 0.041 0.041 0.042 0.038 0.037 0.037 0.037 0.031 0.030 0.029 0.021 0.019 0.019 0.019 0.013 0.012 0.012 0.012 0.008 0.007 0.006 64 128 128 128 128 256 256 256 256 512 512 512 512 0.006