Answered step by step

Verified Expert Solution

Question

1 Approved Answer

3. [4 marks] Oddly-lengthed Stages Instruction execution design might not always result in stages that are equal in length. As an example, consider a system

3. [4 marks] Oddly-lengthed Stages

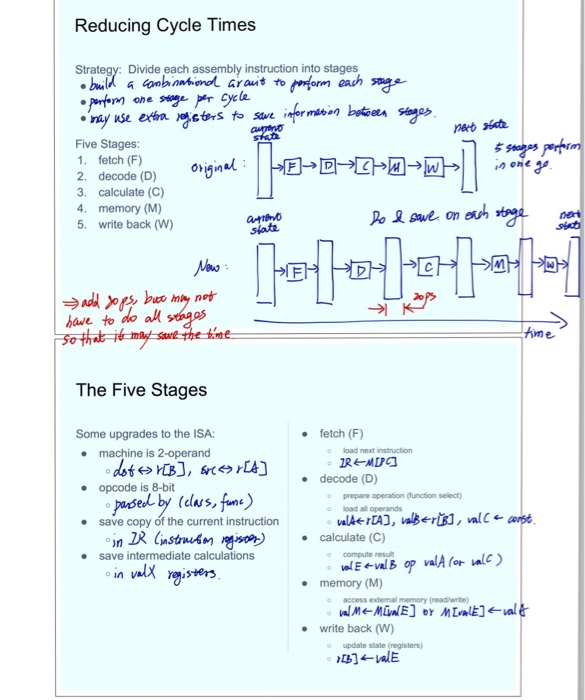

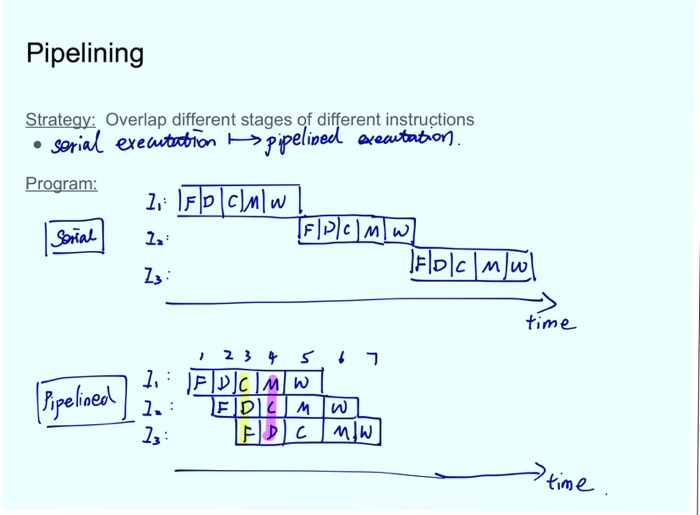

Instruction execution design might not always result in stages that are equal in length.

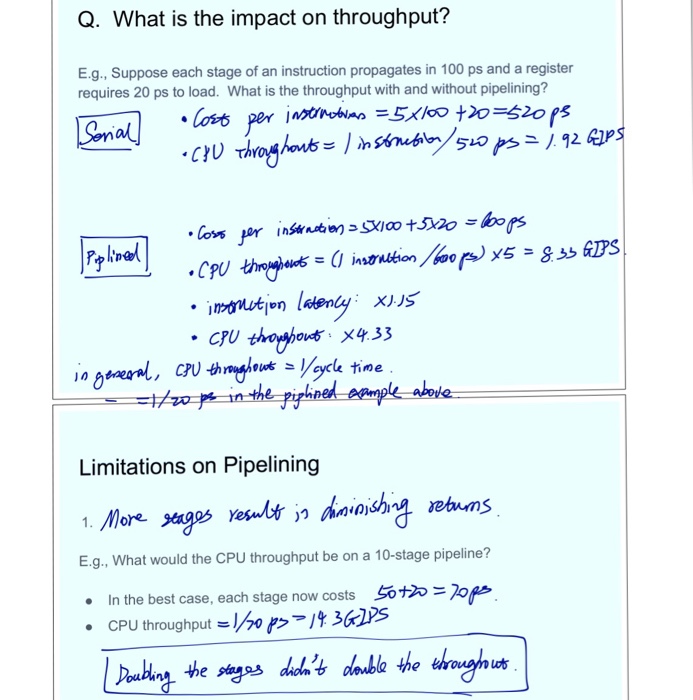

As an example, consider a system that can be cleanly divided into 6 stages, in the order (A, B, C, D, E, F ), each with a propagation delay (in ps) of (110, 220, 190, 200, 100, 80), for a grand total of 900 ps.

The register loading time is 25 ps.

(a) [1 mark] If you only had one extra set of registers to place between an adjacent pair of stages in order to form a 2-stage pipeline, where would you place them? Compute the minimum clock cycle time and the maximum possible CPU throughput.

(b) [1 mark] If you had two extra sets of registers, where would you place them to form a 3-stage pipeline? Again, compute the min clock cycle time and max throughput.

(c) [1 mark] If you had five extra sets of registers, and created a 6-stage pipeline, what would the min clock cycle time and max throughput be?

(d) [1 mark] Suppose you had two extra sets of registers, like in part (b). If you could direct your de- signers to divide any of A, B, C, D, E, F into two stages, where would you tell them to concentrate their efforts?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started