3. The text states that you can combine cycle 1 with cycle 3 in Figure 12.5 to speed up the von Neumann cycle. Can you combine cycle 1 with cycle 2 instead? Explain.

4. The text states that you can decrease the number of cycles from seven to four in Figure 12.5. Write the control signals to fetch the instruction specifier and increment the PC by one with fourcycles.

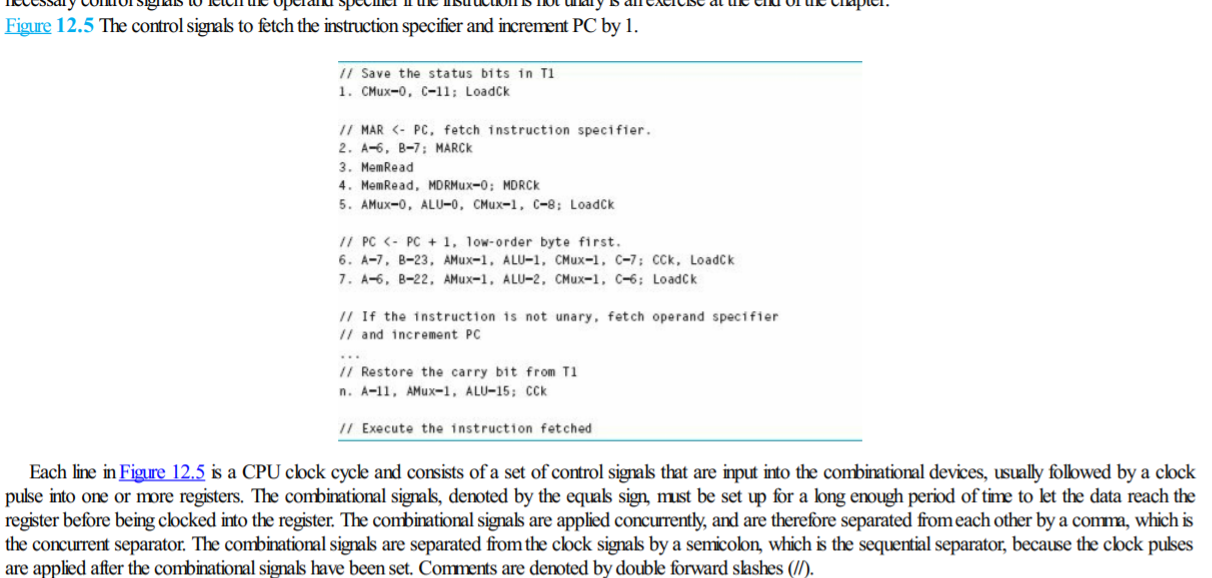

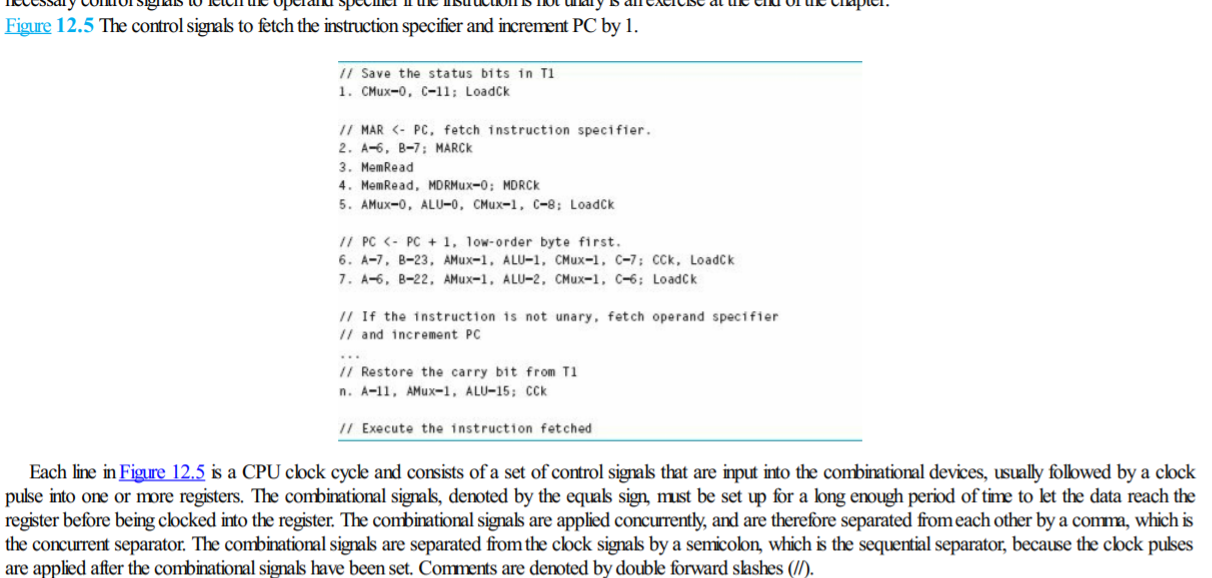

Figure 12.5 The control signals to fetch the instruction specifier and increment PC by 1. 1/ Save the status bits in T1 1. CMux-0, C-11: Loadck 11 MAR (- PC, fetch instruction specifier. 2. A-, B-7; MARCK 3. MemRead 4. MemRead, MD RMux-0; MDRCK 5. AMux-0, ALU-O, CMux-1, C-8; LoadCk // PC - PC +1, low-order byte first. 6. A-7, B-23, AMux-1, ALU-1, CMux-1, C-7; cck, LoadCk 7. A-6, B-22, AMux-1, ALU-2, CMux-1, C-6: LoadCk // If the instruction is not unary, fetch operand specifier // and increment PC // Restore the carry bit from T1 n. A-11, AMux-1, ALU-15; CCK // Execute the instruction fetched Each line in Figure 12.5 is a CPU clock cycle and consists of a set of control signals that are input into the combinational devices, usually followed by a clock pulse into one or more registers. The combinational signals, denoted by the equals sign, must be set up for a long enough period of time to let the data reach the register before being clocked into the register. The combinational signals are applied concurrently, and are therefore separated from each other by a comma, which is the concurrent separator. The combinational signals are separated from the clock signals by a semicolon, which is the sequential separator, because the clock pulses are applied after the combinational signals have been set. Comments are denoted by double forward slashes (II). Figure 12.5 The control signals to fetch the instruction specifier and increment PC by 1. 1/ Save the status bits in T1 1. CMux-0, C-11: Loadck 11 MAR (- PC, fetch instruction specifier. 2. A-, B-7; MARCK 3. MemRead 4. MemRead, MD RMux-0; MDRCK 5. AMux-0, ALU-O, CMux-1, C-8; LoadCk // PC - PC +1, low-order byte first. 6. A-7, B-23, AMux-1, ALU-1, CMux-1, C-7; cck, LoadCk 7. A-6, B-22, AMux-1, ALU-2, CMux-1, C-6: LoadCk // If the instruction is not unary, fetch operand specifier // and increment PC // Restore the carry bit from T1 n. A-11, AMux-1, ALU-15; CCK // Execute the instruction fetched Each line in Figure 12.5 is a CPU clock cycle and consists of a set of control signals that are input into the combinational devices, usually followed by a clock pulse into one or more registers. The combinational signals, denoted by the equals sign, must be set up for a long enough period of time to let the data reach the register before being clocked into the register. The combinational signals are applied concurrently, and are therefore separated from each other by a comma, which is the concurrent separator. The combinational signals are separated from the clock signals by a semicolon, which is the sequential separator, because the clock pulses are applied after the combinational signals have been set. Comments are denoted by double forward slashes (II)