Question

I need to help with the Instruction memory module for a single-cycle processor in Verilog Define the instruction memory as 1024 words of 32bits each

I need to help with the Instruction memory module for a single-cycle processor in Verilog

Define the instruction memory as 1024 words of 32bits each and the data memory as 1024 words of 64bits each

for ARMv8

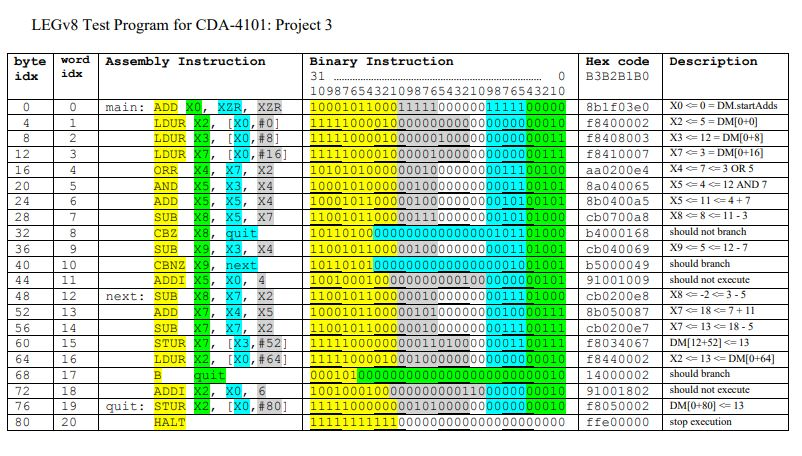

List of opcodes to be supported

LDUR 11111000010 (11)

STUR 11111000000 (11)

ADD 10001011000 (11)

ADDI 1001000100 (10)

SUB 11001011000 (11)

AND 10001010000 (11)

ORR 10101010000 (11)

CBZ 10110100 (8)

CBNZ 10110101 (8)

B 000101 (6)

HALT 11111111111 (11)

Instruction memory

byte value

e0 03 1f 8b 02 00 40 f8 03 80 40 f8 07 00 41 f8 e4 00 02 aa 65 00 04 8a a5 00 04 8b a8 00 07 cb 68 01 00 b4 69 00 04 cb 49 00 00 b5 09 10 00 91 e8 00 02 cb 87 00 05 8b e7 00 02 cb 67 40 03 f8 02 00 44 f8 02 00 00 14 02 18 00 91 02 00 05 f8 00 00 e0 ff

if you need any other information for the project just let me know?

byte idx word idx Assembly Instruction Binary Instruction 31 0 10987654321098765432109876543210 Hex code B3B2B1B0 Description 0 0 main: ADD X0, XZR, XZR 10001011000111110000001111100000 8b1f03e0 X0 LEGV8 Test Program for CDA-4101: Project 3 idx 1 7 byte word Assembly Instruction Binary Instruction Hex code Description idx 31 ........... O B3B2B1BO 10987654321098765432109876543210 0 0 main: ADD XO, XZR, XZR 10001011000111110000001111100000 8b1f03e0X0-0=DM.startAdds 4 LDUR X2, [X0,#0] 11111000010000000000000000000010 48400002X2=5 = DM[0+0] 8 2 LDUR X3, [X0, #8] 11111000010000001000000000000011 18408003 X3 = 12 = DM[0+8) 12 3 LDUR X7, [X0, #16] 11111000010000010000000000000111 18410007X7 =3 = DM[0+16 4 ORR 10101010000000100000000011100100aa0200e4X4=7=3 OR 5 5 AND X5, X3, X4 10001010000001000000000001100101 8a040065X54 =12 AND 7 6 ADD X5, X4 10001011000001000000000010100101 8b0400a5 X5 -11 =4+7 SUB X5, X7 11001011000001110000000010101000 cb0700a8X8=8=11-3 CBZ quit 10110100000000000000000101101000b4000168 should not branch SUB X3, X4 11001011000001000000000001101001 cb040069 X95=12-7 CBN: next 10110101000000000000000001001001b5000049should branch ADD XO, 4 10010001000000000001000000000101 91001009 should not execute 12 SUE X7, 11001011000000100000000011101000 cb0200e8X8 = -2 -3-5 ADD 10001011000001010000000010000111 | 8b050087 X7-18=7+11 11001011000000100000000011100111 | cb0200e7X7 - 13 = 18-5 STUR 521 11111000000000110100000001100111 | 18034067 DM[12+52]

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started