Question

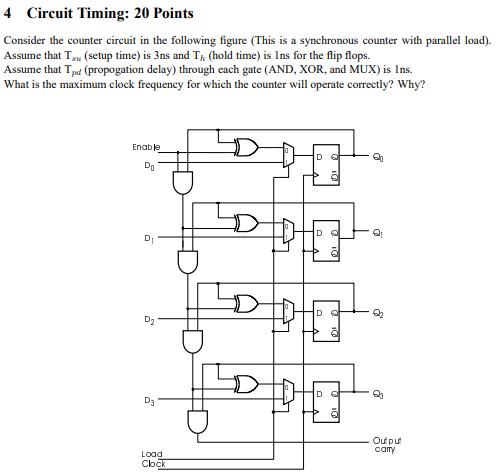

4 Circuit Timing: 20 Points Consider the counter circuit in the following figure (This is a synchronous counter with parallel load). Assume that T,

4 Circuit Timing: 20 Points Consider the counter circuit in the following figure (This is a synchronous counter with parallel load). Assume that T, (setup time) is 3ns and T, (hold time) is Ins for the flip flops. Assume that Tpd (propogation delay) through each gate (AND, XOR, and MUX) is Ins. What is the maximum clock frequency for which the counter will operate correctly? Why? Enable Do D. D2 D3 Out put cary Load Clock

Step by Step Solution

3.55 Rating (145 Votes )

There are 3 Steps involved in it

Step: 1

S01a consider the tollowing data Propogahian dalay ...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Physics for Scientists and Engineers A Strategic Approach with Modern Physics

Authors: Randall D. Knight

4th edition

978-0134092508, 134092503, 133942651, 978-0133942651

Students also viewed these Electrical Engineering questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App