Answered step by step

Verified Expert Solution

Question

1 Approved Answer

4 Write the VHDL with select when statement for the output of the majority circuit. The with select when statement, also known as the selected

4

-

Write the VHDL with select when statement for the output of the majority circuit. The with select when statement, also known as the selected signal assignment statement, is based on the truth table for the circuit.

The syntax for, and a detailed description of, the VHDL with select when the statement is provided in Section X.X.X, below, and in Appendix A of your textbook.

Boolean Expression:

VHDL Code (signal assignment statement):

VHDL Code (with select when statement):

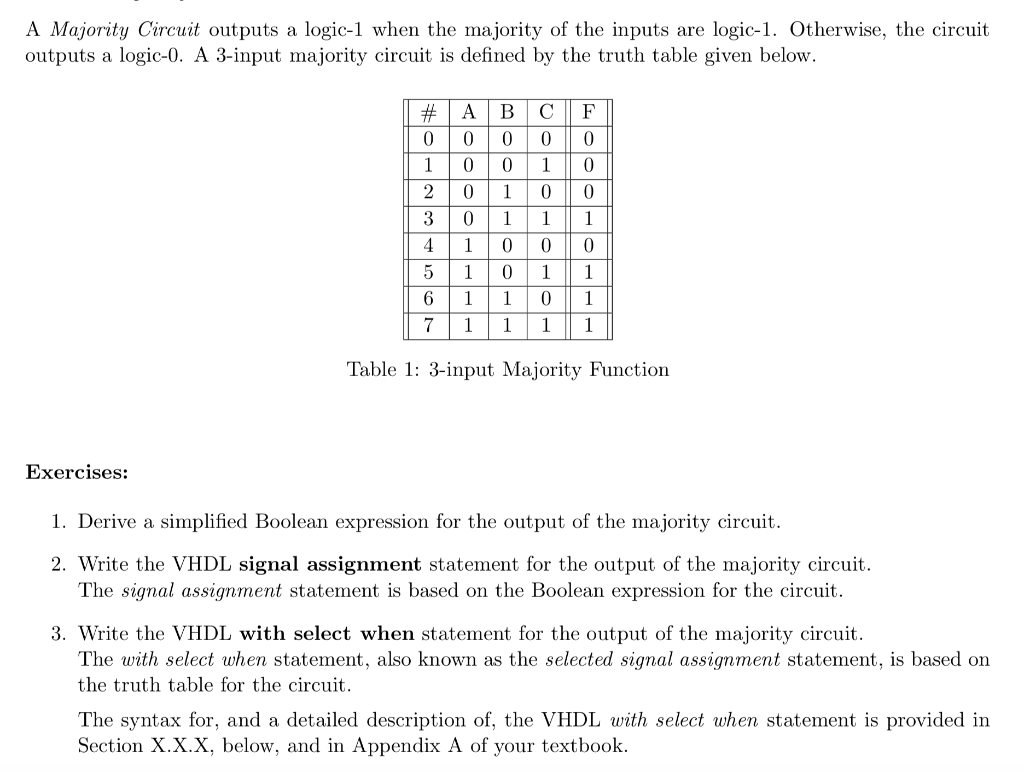

A Majority Circuit outputs a logic-1 when the majority of the inputs are logic-1. Otherwise, the circuit outputs a logic-0. A 3-input majority circuit is defined by the truth table given below. | | # 0 A B C F 0 0 0 0 0 01 0 011 1 0 0 | 1 0 1 1 1 0 1 1 1 6 7 1 Table 1: 3-input Majority Function Exercises: 1. Derive a simplified Boolean expression for the output of the majority circuit. 2. Write the VHDL signal assignment statement for the output of the majority circuit. The signal assignment statement is based on the Boolean expression for the circuit. 3. Write the VHDL with select when statement for the output of the majority circuit. The with select when statement, also known as the selected signal assignment statement, is based on the truth table for the circuit. The syntax for, and a detailed description of, the VHDL with select when statement is provided in Section X.X.X, below, and in Appendix A of your textbook. A Majority Circuit outputs a logic-1 when the majority of the inputs are logic-1. Otherwise, the circuit outputs a logic-0. A 3-input majority circuit is defined by the truth table given below. | | # 0 A B C F 0 0 0 0 0 01 0 011 1 0 0 | 1 0 1 1 1 0 1 1 1 6 7 1 Table 1: 3-input Majority Function Exercises: 1. Derive a simplified Boolean expression for the output of the majority circuit. 2. Write the VHDL signal assignment statement for the output of the majority circuit. The signal assignment statement is based on the Boolean expression for the circuit. 3. Write the VHDL with select when statement for the output of the majority circuit. The with select when statement, also known as the selected signal assignment statement, is based on the truth table for the circuit. The syntax for, and a detailed description of, the VHDL with select when statement is provided in Section X.X.X, below, and in Appendix A of your textbookStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started