Question: 4.3. When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. Assume we start with datapath

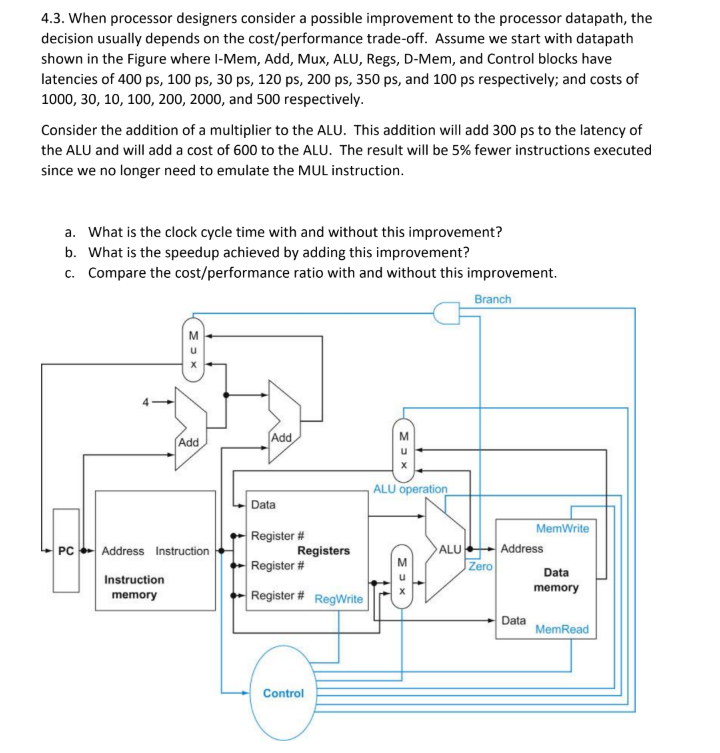

4.3. When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. Assume we start with datapath shown in the Figure where I-Mem, Add, Mux, ALU, Regs, D-Mem, and Control blocks have latencies of 400 ps, 100 ps, 30 ps, 120 ps, 200 ps, 350 ps, and 100 ps respectively; and costs of 1000, 30, 10, 100, 200, 2000, and 500 respectively. Consider the addition of a multiplier to the ALU. This addition will add 300 ps to the latency of the ALU and will add a cost of 600 to the ALU. The result will be 5% fewer instructions executed since we no longer need to emulate the MUL instruction. a. What is the clock cycle time with and without this improvement? b. What is the speedup achieved by adding this improvement? C. Compare the cost/performance ratio with and without this improvement. Branch ALU operation Data MemWrite PC Address Instruction Register # Registers Register # ALU - Zero Address Data memory Instruction memory Register # RegWrite Data MemRead Control 4.2. The basic single-cycle MIPS implementation in Figure 1 can only implement some instructions. New instructions can be added to an existing Instructions Set Architecture (ISA), but the decision whether or not to do that depends, among other things, on the cost and complexity the proposed addition introduces into the processor datapath and control. Consider the new instruction LWI given below: Instruction: LWI Rt, Rd(Rs) Interpretation: Reg[Rt] = Mem[Reg(Rd] + Reg[Rs]] a. Which existing blocks (if any) can be used for this instruction? b. Which new functional blocks (if any) do we need for this instruction? c. What new signals do we need (if any) from the control unit to support this instruction? 4.3. When processor designers consider a possible improvement to the processor datapath, the decision usually depends on the cost/performance trade-off. Assume we start with datapath shown in the Figure where I-Mem, Add, Mux, ALU, Regs, D-Mem, and Control blocks have latencies of 400 ps, 100 ps, 30 ps, 120 ps, 200 ps, 350 ps, and 100 ps respectively; and costs of 1000, 30, 10, 100, 200, 2000, and 500 respectively. Consider the addition of a multiplier to the ALU. This addition will add 300 ps to the latency of the ALU and will add a cost of 600 to the ALU. The result will be 5% fewer instructions executed since we no longer need to emulate the MUL instruction. a. What is the clock cycle time with and without this improvement? b. What is the speedup achieved by adding this improvement? C. Compare the cost/performance ratio with and without this improvement. Branch ALU operation Data MemWrite PC Address Instruction Register # Registers Register # ALU - Zero Address Data memory Instruction memory Register # RegWrite Data MemRead Control 4.2. The basic single-cycle MIPS implementation in Figure 1 can only implement some instructions. New instructions can be added to an existing Instructions Set Architecture (ISA), but the decision whether or not to do that depends, among other things, on the cost and complexity the proposed addition introduces into the processor datapath and control. Consider the new instruction LWI given below: Instruction: LWI Rt, Rd(Rs) Interpretation: Reg[Rt] = Mem[Reg(Rd] + Reg[Rs]] a. Which existing blocks (if any) can be used for this instruction? b. Which new functional blocks (if any) do we need for this instruction? c. What new signals do we need (if any) from the control unit to support this instruction

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts