Question: A computer has 16 GB of byte-addressable main memory space. It is proposed to design a 256 KB L1 cache memory with a refill line

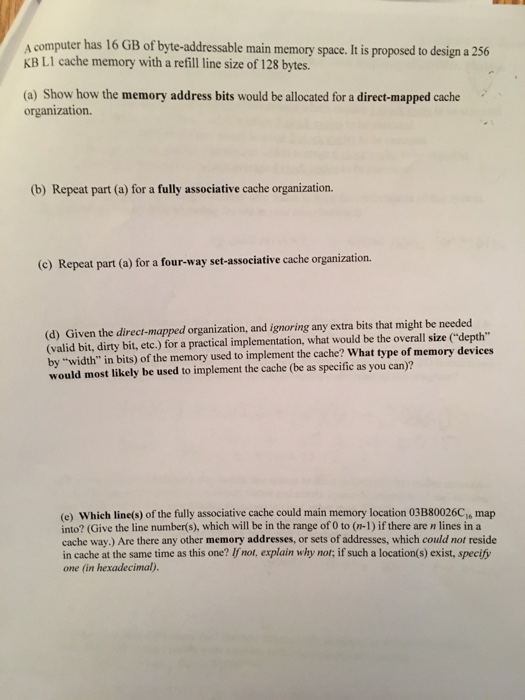

A computer has 16 GB of byte-addressable main memory space. It is proposed to design a 256 KB L1 cache memory with a refill line size of 128 bytes. Show how the memory address bits would be allocated for a direct-mapped cache organization. Repeat part (a) for a fully associative cache organization. Repeat part (a) for a four-way set-associative cache organization. Given the direct-mapped organization, and ignoring any extra bits that might be needed (valid bit, dirty bit, etc) for a practical implementation, what would be the overall size ("depth" by "width" in bits) type of memory devices of the memory used to implement the cache? What would most likely be used to implement the cache (be as specific as you can)? Which line(s) of the fully associative cache could main memory location 03B80026C_16 map into? (Give the line number(s), which will be in the range of 0 to (n - 1) if there are n lines in a cache way. Are there any other memory addresses, or sets of addresses, which could not reside in cache at the same time as this one? If not, explain why not; if such a location(s) exist, specify one (in hexadecimal)

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts