a. P15: read 120

b. P15: read 118

P15: write 110

P15: write 130

c. P:1 read 110

P1: read 108

P1: read 130

d. P0: read 100

P0: write 108

P0: write 128

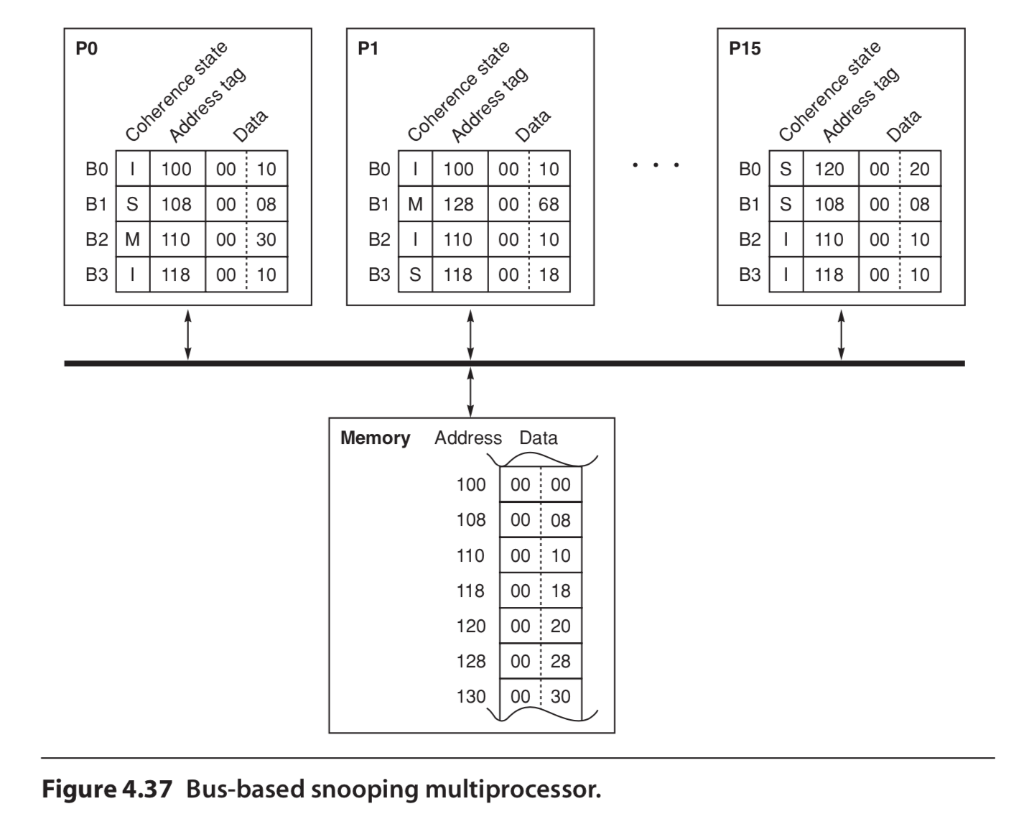

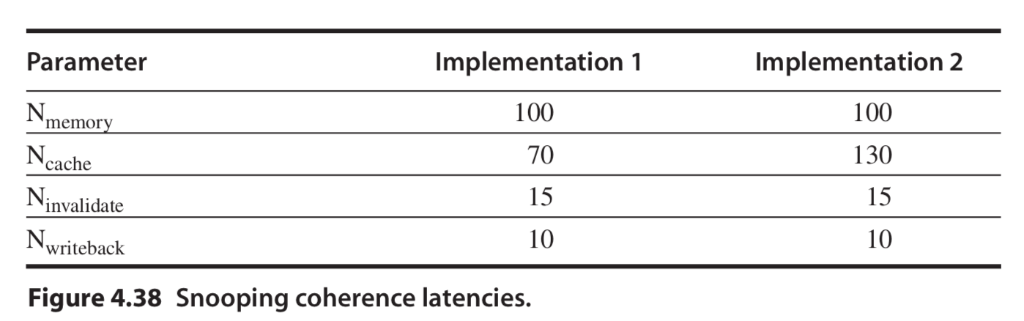

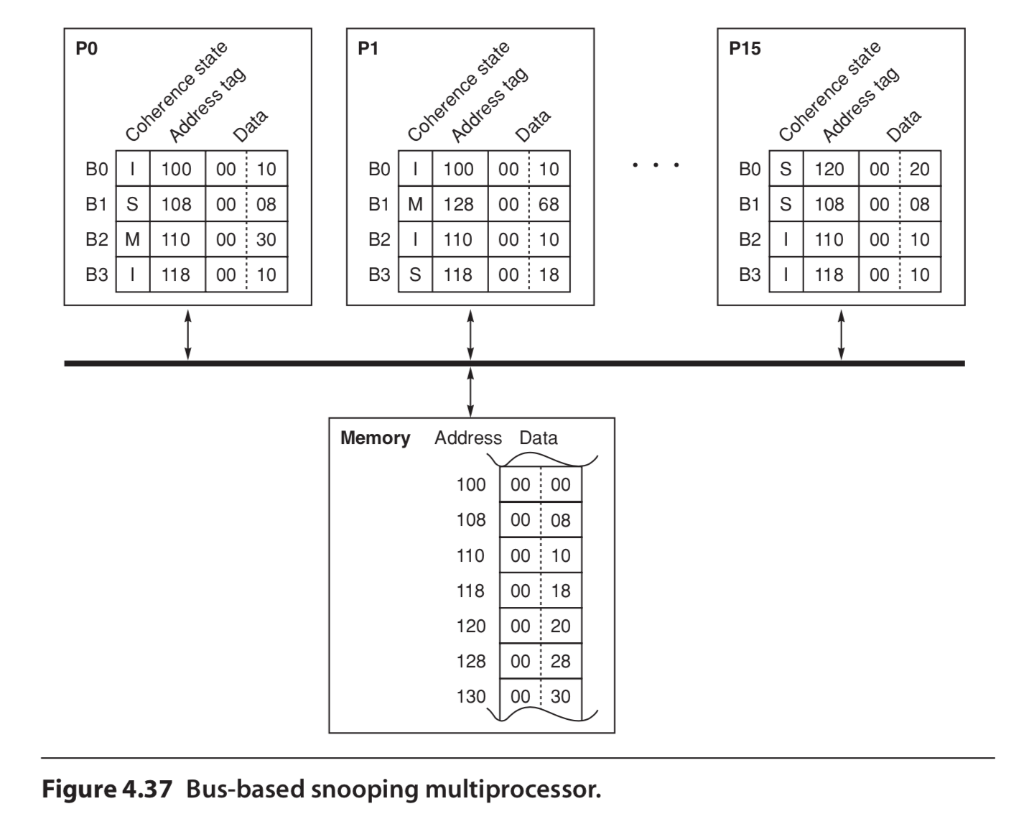

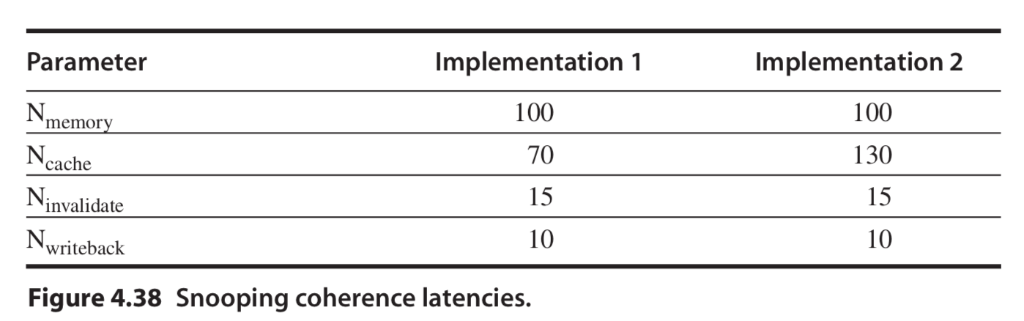

CPU write hits that generate an invalidate incur Ninvalidate stall cycles. - a writeback of a block, either due to a conflict or another processor's re quest to an exclusive block, incurs an additional Nwriteback stall cycles. Consider two implementations with different performance characteristics sum marized in Figure 4.38. Consider the following sequence of operations assuming the initial cache state in Figure 4.37. For simplicity, assume that the second operation begins after the first completes (even though they are on different processors): P1: read 110 P15: read 110 For Implementation 1, the first read generates 80 stall cycles because the read is satisfied by PO's cache. Pl stalls for 70 cycles while it waits for the block, and PO stalls for 10 cycles while it writes the block back to memory in response to PI's request. Thus the second read by P15 generates 100 stall cycles because its miss is satisfied by memory. Thus this sequence generates a total of 180 stall cycles. For the following sequences of operations, how many stall cycles are generated by each implementation? CPU write hits that generate an invalidate incur Ninvalidate stall cycles. - a writeback of a block, either due to a conflict or another processor's re quest to an exclusive block, incurs an additional Nwriteback stall cycles. Consider two implementations with different performance characteristics sum marized in Figure 4.38. Consider the following sequence of operations assuming the initial cache state in Figure 4.37. For simplicity, assume that the second operation begins after the first completes (even though they are on different processors): P1: read 110 P15: read 110 For Implementation 1, the first read generates 80 stall cycles because the read is satisfied by PO's cache. Pl stalls for 70 cycles while it waits for the block, and PO stalls for 10 cycles while it writes the block back to memory in response to PI's request. Thus the second read by P15 generates 100 stall cycles because its miss is satisfied by memory. Thus this sequence generates a total of 180 stall cycles. For the following sequences of operations, how many stall cycles are generated by each implementation