Answered step by step

Verified Expert Solution

Question

1 Approved Answer

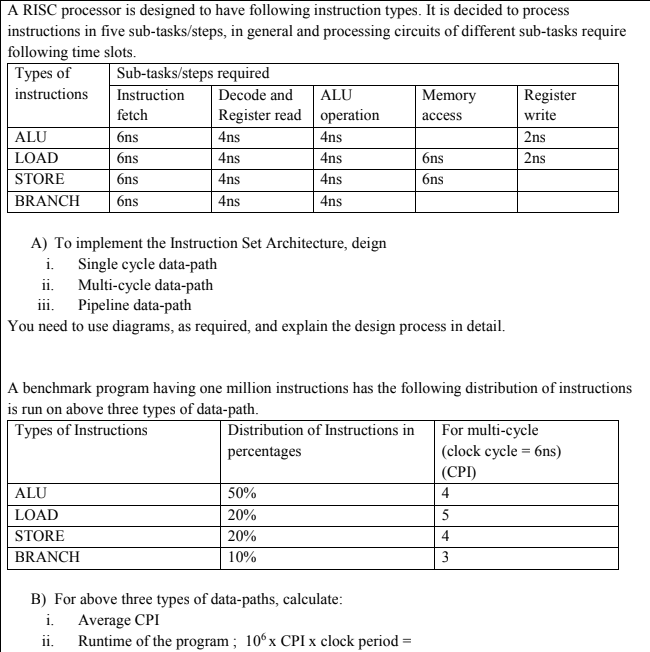

A RISC processor is designed to have following instruction types. It is decided to process instructions in five sub-tasks/steps, in general and processing circuits

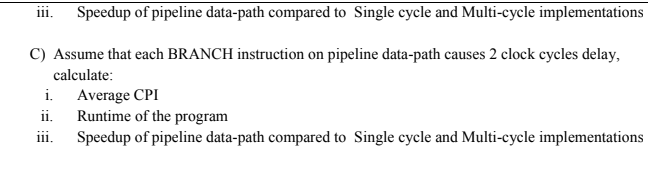

A RISC processor is designed to have following instruction types. It is decided to process instructions in five sub-tasks/steps, in general and processing circuits of different sub-tasks require following time slots. Types of instructions Sub-tasks/steps required Instruction fetch ALU 6ns LOAD 6ns STORE 6ns BRANCH 6ns Decode and Register read 4ns 4ns 4ns 4ns ALU LOAD STORE BRANCH ALU operation 4ns 4ns 4ns 4ns A) To implement the Instruction Set Architecture, deign i. Single cycle data-path ii. Multi-cycle data-path iii. Pipeline data-path You need to use diagrams, as required, and explain the design process in detail. 50% 20% 20% 10% Distribution of Instructions in percentages Memory access 6ns 6ns A benchmark program having one million instructions has the following distribution of instructions is run on above three types of data-path. Types of Instructions B) For above three types of data-paths, calculate: i. Average CPI ii. Runtime of the program; 106 x CPI x clock period = Register write 2ns 2ns For multi-cycle (clock cycle = 6ns) (CPI) 4 5 4 3 iii. Speedup of pipeline data-path compared to Single cycle and Multi-cycle implementations C) Assume that each BRANCH instruction on pipeline data-path causes 2 clock cycles delay, calculate: i. Average CPI ii. 111. Runtime of the program Speedup of pipeline data-path compared to Single cycle and Multi-cycle implementations

Step by Step Solution

★★★★★

3.45 Rating (164 Votes )

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started