Answered step by step

Verified Expert Solution

Question

1 Approved Answer

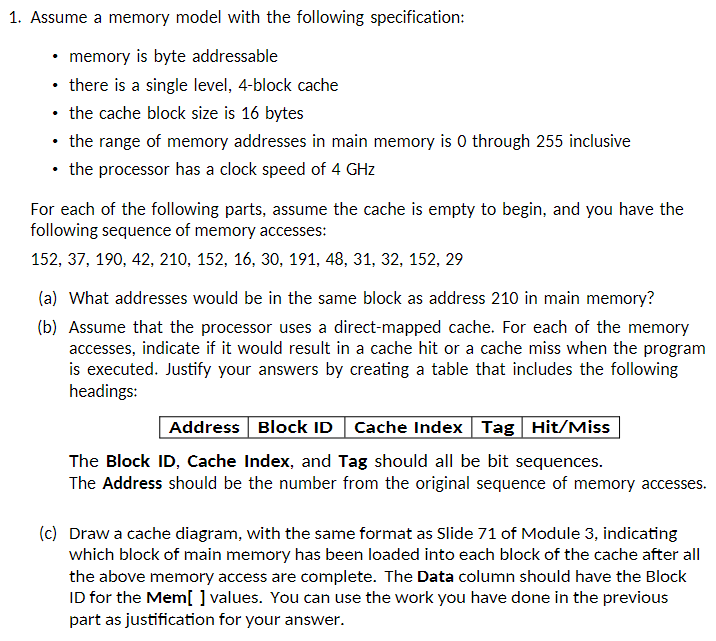

Assume a memory model with the following specification: memory is byte addressable there is a single level, 4 - block cache the cache block size

Assume a memory model with the following specification:

memory is byte addressable

there is a single level, block cache

the cache block size is bytes

the range of memory addresses in main memory is through inclusive

the processor has a clock speed of

For each of the following parts, assume the cache is empty to begin, and you have the

following sequence of memory accesses:

a What addresses would be in the same block as address in main memory?

b Assume that the processor uses a directmapped cache. For each of the memory

accesses, indicate if it would result in a cache hit or a cache miss when the program

is executed. Justify your answers by creating a table that includes the following

headings:

The Block ID Cache Index, and Tag should all be bit sequences.

The Address should be the number from the original sequence of memory accesses.

c Draw a cache diagram, with the same format as Slide of Module indicating

which block of main memory has been loaded into each block of the cache after all

the above memory access are complete. The Data column should have the Block

ID for the Mem values. You can use the work you have done in the previous

part as justification for your answer.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started