Answered step by step

Verified Expert Solution

Question

1 Approved Answer

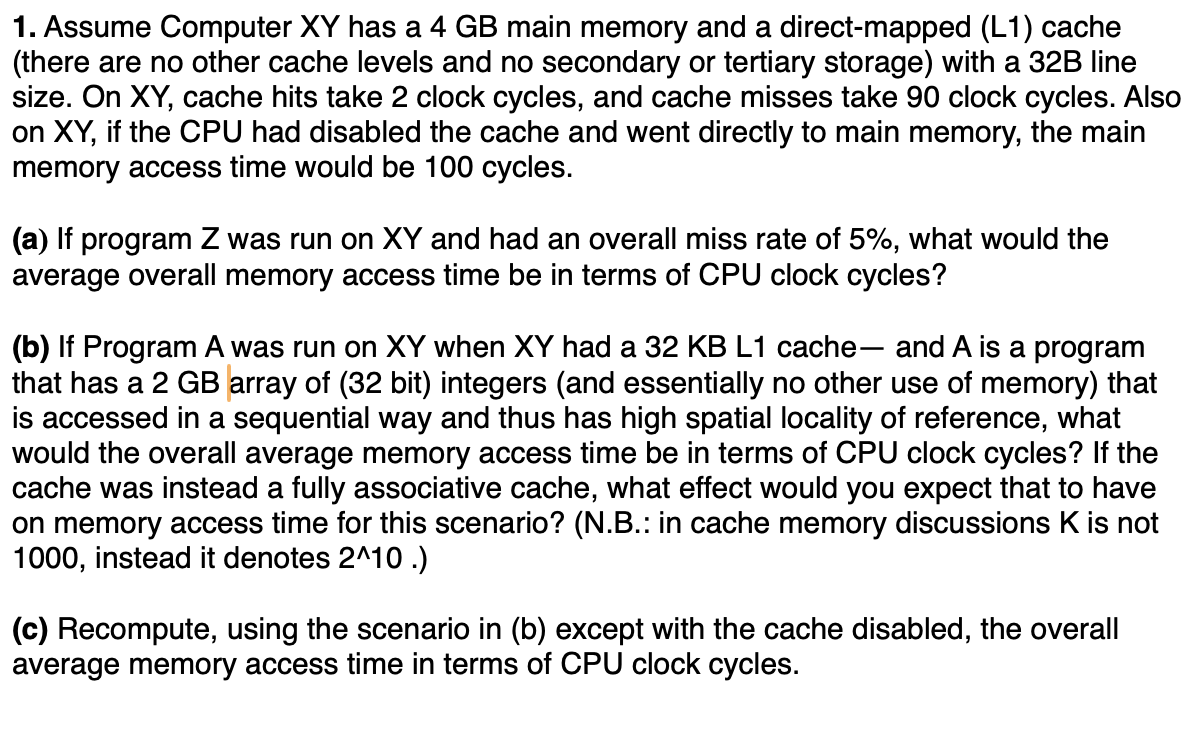

Assume Computer XY has a 4 GB main memory and a direct - mapped ( L 1 ) cache ( there are no other cache

Assume Computer XY has a GB main memory and a directmapped L cache

there are no other cache levels and no secondary or tertiary storage with a B line

size. On XY cache hits take clock cycles, and cache misses take clock cycles. Also

on XY if the CPU had disabled the cache and went directly to main memory, the main

memory access time would be cycles.

a If program was run on and had an overall miss rate of what would the

average overall memory access time be in terms of CPU clock cycles?

b If Program A was run on XY when XY had a cache and is a program

that has a GB array of bit integers and essentially no other use of memory that

is accessed in a sequential way and thus has high spatial locality of reference, what

would the overall average memory access time be in terms of CPU clock cycles? If the

cache was instead a fully associative cache, what effect would you expect that to have

on memory access time for this scenario? NB: in cache memory discussions K is not

instead it denotes

c Recompute, using the scenario in b except with the cache disabled, the overall

average memory access time in terms of CPU clock cycles.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started