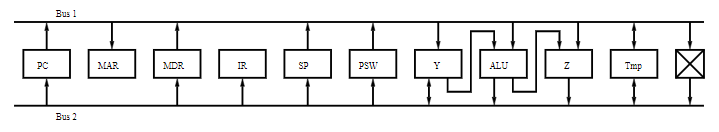

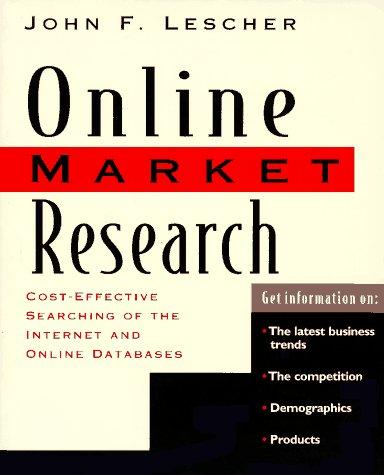

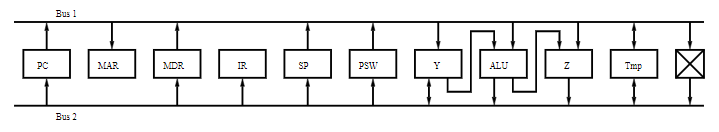

Bus 1 PC MAR MDR IR SP PSW ALU Tmp Bus 2 Assume that the company that you are employed is developing a hardwired control unit for a new processor. Given the above data path, synthesize the sequence of control signals to solve the following instruction set implementation problems. Assume that the cross connecting the two buses (effectively making it one large bus), is enabled with the control signal CROSS. (a) Develop the control signals to fetch instructions from memory; the instruction set architecture has two instruction formats, one is 1 byte long and the second is 2 bytes long. The leftmost bit in the instruction defines if it is 1 byte (leftmost bit=0) or 2 bytes (leftmost bit=1) long. You must ensure that the entire instruction is read into the instruction register (IR). Since you will require some type of condition testing to decide between one and two byte instructions, informally explain how this could be achieved. (b) Assume that this architecture performs effective address computations following the algorithm: EA = second byte in the IR if IR.R = 1 then EA = EA + PC if IR.I - 1 then EA = MMEA] Show the control signals for 3 separate states that perform the function of each line in the above algorithm. Draw the state machine and the corresponding transitions that would move through these states from a fetch state to an execute state. Bus 1 PC MAR MDR IR SP PSW ALU Tmp Bus 2 Assume that the company that you are employed is developing a hardwired control unit for a new processor. Given the above data path, synthesize the sequence of control signals to solve the following instruction set implementation problems. Assume that the cross connecting the two buses (effectively making it one large bus), is enabled with the control signal CROSS. (a) Develop the control signals to fetch instructions from memory; the instruction set architecture has two instruction formats, one is 1 byte long and the second is 2 bytes long. The leftmost bit in the instruction defines if it is 1 byte (leftmost bit=0) or 2 bytes (leftmost bit=1) long. You must ensure that the entire instruction is read into the instruction register (IR). Since you will require some type of condition testing to decide between one and two byte instructions, informally explain how this could be achieved. (b) Assume that this architecture performs effective address computations following the algorithm: EA = second byte in the IR if IR.R = 1 then EA = EA + PC if IR.I - 1 then EA = MMEA] Show the control signals for 3 separate states that perform the function of each line in the above algorithm. Draw the state machine and the corresponding transitions that would move through these states from a fetch state to an execute state