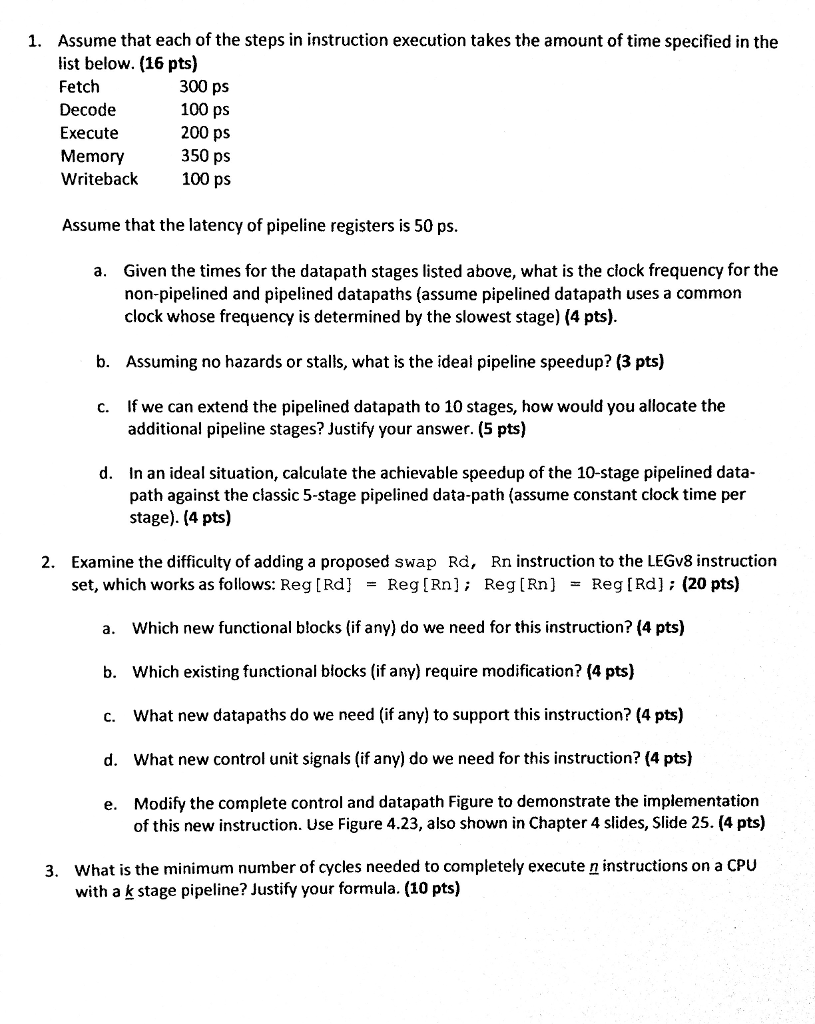

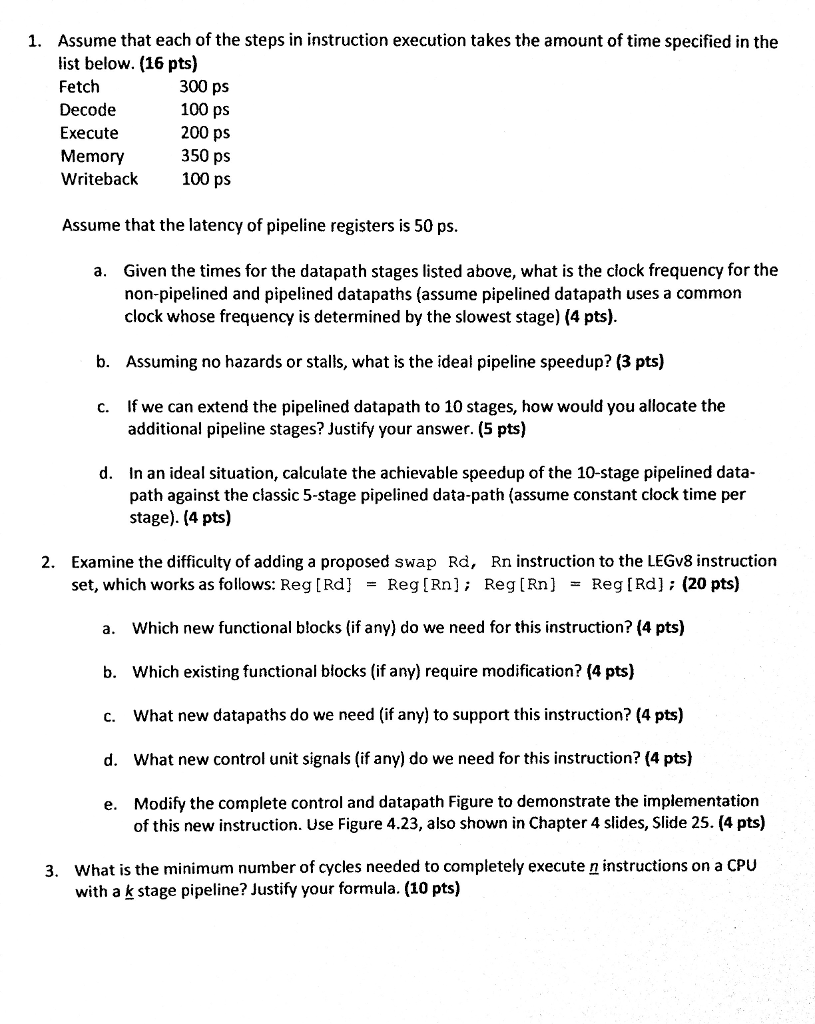

Can you please solve all 3 questions and show your work.

Assume that each of the steps in instruction execution takes the amount of time specified in the list below. (16 pts) Fetch Decode Execute Memory Writeback 1. 300 ps 100 ps 200 ps 350 ps 100 ps Assume that the latency of pipeline registers is 50 ps Given the times for the datapath stages listed above, what is the clock frequency for the non-pipelined and pipelined datapaths (assume pipelined datapath uses a common clock whose frequency is determined by the slowest stage) (4 pts) a. b. Assuming no hazards or stalls, what is the ideal pipeline speedup? (3 pts) If we can extend the pipelined datapath to 10 stages, how would you allocate the additional pipeline stages? Justify your answer. (5 pts) c. In an ideal situation, calculate the achievable speedup of the 10-stage pipelined data- path against the classic 5-stage pipelined data-path (assume constant clock time per stage). (4 pts) d. Examine the difficulty of adding a proposed swap Rd, Rn instruction to the LEGv8 instruction set, which works as follows: Reg [Rd] = Reg [Rn] ; Reg [Rn] = Reg [Rd] ; (20 pts) 2. a. Which new functional blocks (if any) do we need for this instruction? (4 pts) b. Which existing functional blocks (if any) require modification? (4 pts) c. What new datapaths do we need (if any) to support this instruction? (4 pts) d. What new control unit signals (if any) do we need for this instruction? (4 pts) e. Modify the complete control and datapath Figure to demonstrate the implementation of this new instruction. Use Figure 4.23, also shown in Chapter 4 slides, Slide 25. (4 pts) What is the minimum number of cycles needed to completely execute n instructions on a CPU with a k stage pipeline? Justify your formula. (10 pts) 3. Assume that each of the steps in instruction execution takes the amount of time specified in the list below. (16 pts) Fetch Decode Execute Memory Writeback 1. 300 ps 100 ps 200 ps 350 ps 100 ps Assume that the latency of pipeline registers is 50 ps Given the times for the datapath stages listed above, what is the clock frequency for the non-pipelined and pipelined datapaths (assume pipelined datapath uses a common clock whose frequency is determined by the slowest stage) (4 pts) a. b. Assuming no hazards or stalls, what is the ideal pipeline speedup? (3 pts) If we can extend the pipelined datapath to 10 stages, how would you allocate the additional pipeline stages? Justify your answer. (5 pts) c. In an ideal situation, calculate the achievable speedup of the 10-stage pipelined data- path against the classic 5-stage pipelined data-path (assume constant clock time per stage). (4 pts) d. Examine the difficulty of adding a proposed swap Rd, Rn instruction to the LEGv8 instruction set, which works as follows: Reg [Rd] = Reg [Rn] ; Reg [Rn] = Reg [Rd] ; (20 pts) 2. a. Which new functional blocks (if any) do we need for this instruction? (4 pts) b. Which existing functional blocks (if any) require modification? (4 pts) c. What new datapaths do we need (if any) to support this instruction? (4 pts) d. What new control unit signals (if any) do we need for this instruction? (4 pts) e. Modify the complete control and datapath Figure to demonstrate the implementation of this new instruction. Use Figure 4.23, also shown in Chapter 4 slides, Slide 25. (4 pts) What is the minimum number of cycles needed to completely execute n instructions on a CPU with a k stage pipeline? Justify your formula. (10 pts) 3