Question

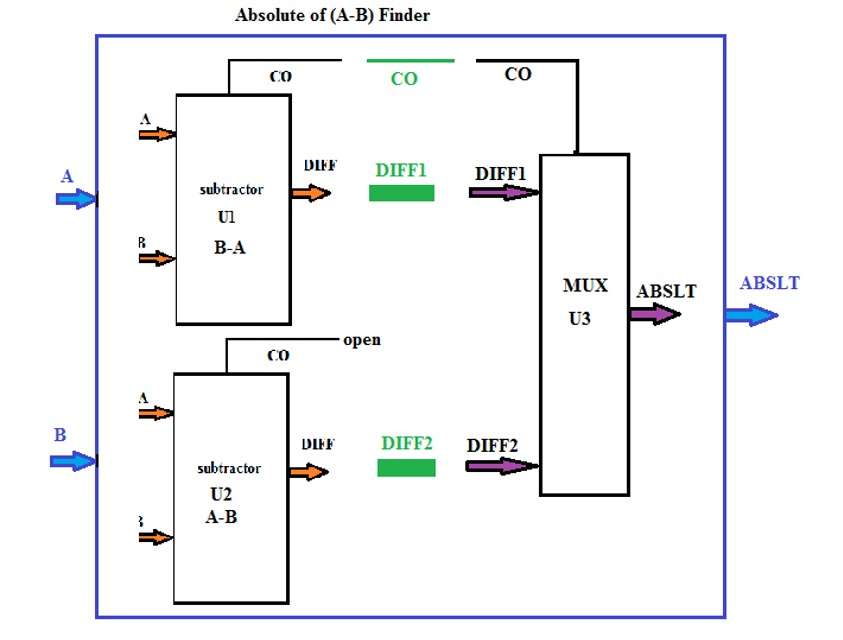

Complete the VHDL code below to the parts together as shown below: --tie.vhd library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; --------------------------------------------------- entity tie isport

Complete the VHDL code below to the parts together as shown below:

--tie.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

---------------------------------------------------

entity tie isport ( A,B: ___ _______________________; --inputs in blue

ABSLT: ___ _______________________); -- outputs in blue

end tie;

---------------------------------------------------

architecture behv of tie is

signal ______ , _____ : _________________________ ; -- tie vector wires in green

signal _____: ________; -- single wire in green

begin

U1: entity work.subtractor port map ( _ => _ , _ => _ , ____ => _____ , __ => __ ); -- tie unit 1

U2: entity work.subtractor port map ( _ => _ , _ => _ , ____ => ____ , CO => open); -- tie unit 2

U3: entity work.mux port map (_____ => _____ , _____ => _____ , _____=> _____ , __ => __ );

end behv;

--subtractor.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

---------------------------------------------------

entity subtractor is

port( A,B: in std_logic_vector(4 downto 0);

DIFF: out std_logic_vector(4 downto 0);

CO: out std_logic );

end subtractor;

---------------------------------------------------

architecture behv of subtractor is

begin

DIFF

CO

end behv;

--mux.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

-------------------------------------------------

entity mux is port

(DIFF1, DIFF2: in std_logic_vector(4 downto 0);

ABSLT:out std_logic_vector(4 downto 0);

CO:in std_logic);

end mux;

-------------------------------------------------

architecture behv of mux is

begin

with CO select ABSLT

DIFF1when '0',-- a CO=0 selects B-A

DIFF2when '1', -- a CO=1 selects A-B

"ZZZZZ" when others; -- high impedance otherwise

end behv;

--testbench.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

---------------------------------------------------

entity tie_tb is

end tie_tb;

---------------------------------------------------

architecture behv of tie_tb is

signalA, B: std_logic_vector(4 downto 0);

signal ABSLT: std_logic_vector(4 downto 0);

begin

U1: entity work.tie port map (A => A, B => B, ABSLT => ABSLT);

--apply Stimulus Signals to A and B

A

B

end behv;

Absolute of (A-B) Finder CO co Co DIF DIFF DIFFI Ul .ABSLT |.ABSLT open Co DIFF2 DIFF2 U2 A-B Absolute of (A-B) Finder CO co Co DIF DIFF DIFFI Ul .ABSLT |.ABSLT open Co DIFF2 DIFF2 U2 A-BStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started