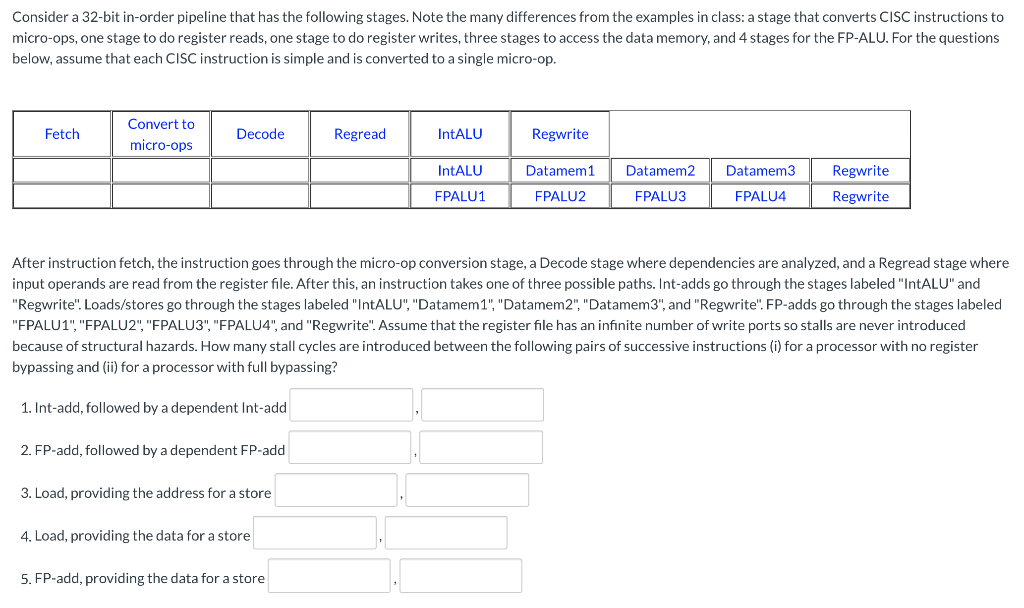

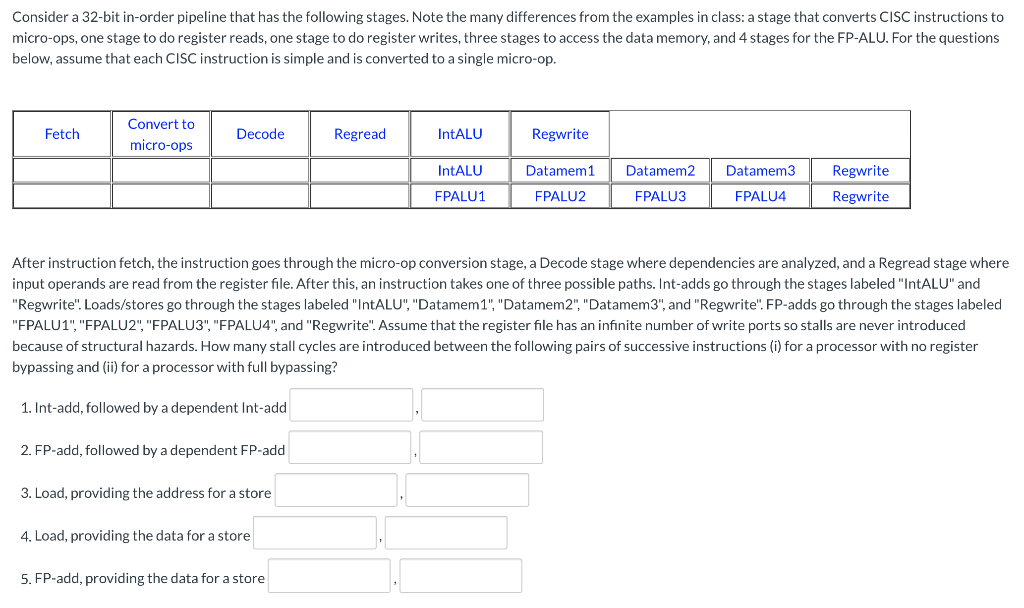

Consider a 32-bit in-order pipeline that has the following stages. Note the many differences from the examples in class: a stage that converts CISC instructions to micro-ops, one stage to do register reads, one stage to do register writes, three stages to access the data memory, and 4 stages for the FP-ALU. For the questions below, assume that each CISC instruction is simple and is converted to a single micro-op. Fetch Convert to micro-ops Decode Regread IntALU Regwrite Regwrite IntALU FPALU1 Datamem 1 FPALU2 Datamem2 FPALU3 Datamem3 F PALU4 Regwrite After instruction fetch, the instruction goes through the micro-op conversion stage, a Decode stage where dependencies are analyzed, and a Regread stage where input operands are read from the register file. After this, an instruction takes one of three possible paths. Int-adds go through the stages labeled "IntALU" and "Regwrite". Loads/stores go through the stages labeled "IntALU", "Datamem 1", "Datamem2","Datamem3", and "Regwrite". FP-adds go through the stages labeled "EPALU1", "FPALU2", "FPALU3", "FPALU4", and "Regwrite". Assume that the register file has an infinite number of write ports so stalls are never introduced because of structural hazards. How many stall cycles are introduced between the following pairs of successive instructions (i) for a processor with no register bypassing and (ii) for a processor with full bypassing? 1. Int-add, followed by a dependent Int-add 2. FP-add, followed by a dependent FP-add 3. Load, providing the address for a store 4. Load, providing the data for a store 5. FP-add, providing the data for a store Consider a 32-bit in-order pipeline that has the following stages. Note the many differences from the examples in class: a stage that converts CISC instructions to micro-ops, one stage to do register reads, one stage to do register writes, three stages to access the data memory, and 4 stages for the FP-ALU. For the questions below, assume that each CISC instruction is simple and is converted to a single micro-op. Fetch Convert to micro-ops Decode Regread IntALU Regwrite Regwrite IntALU FPALU1 Datamem 1 FPALU2 Datamem2 FPALU3 Datamem3 F PALU4 Regwrite After instruction fetch, the instruction goes through the micro-op conversion stage, a Decode stage where dependencies are analyzed, and a Regread stage where input operands are read from the register file. After this, an instruction takes one of three possible paths. Int-adds go through the stages labeled "IntALU" and "Regwrite". Loads/stores go through the stages labeled "IntALU", "Datamem 1", "Datamem2","Datamem3", and "Regwrite". FP-adds go through the stages labeled "EPALU1", "FPALU2", "FPALU3", "FPALU4", and "Regwrite". Assume that the register file has an infinite number of write ports so stalls are never introduced because of structural hazards. How many stall cycles are introduced between the following pairs of successive instructions (i) for a processor with no register bypassing and (ii) for a processor with full bypassing? 1. Int-add, followed by a dependent Int-add 2. FP-add, followed by a dependent FP-add 3. Load, providing the address for a store 4. Load, providing the data for a store 5. FP-add, providing the data for a store