Answered step by step

Verified Expert Solution

Question

1 Approved Answer

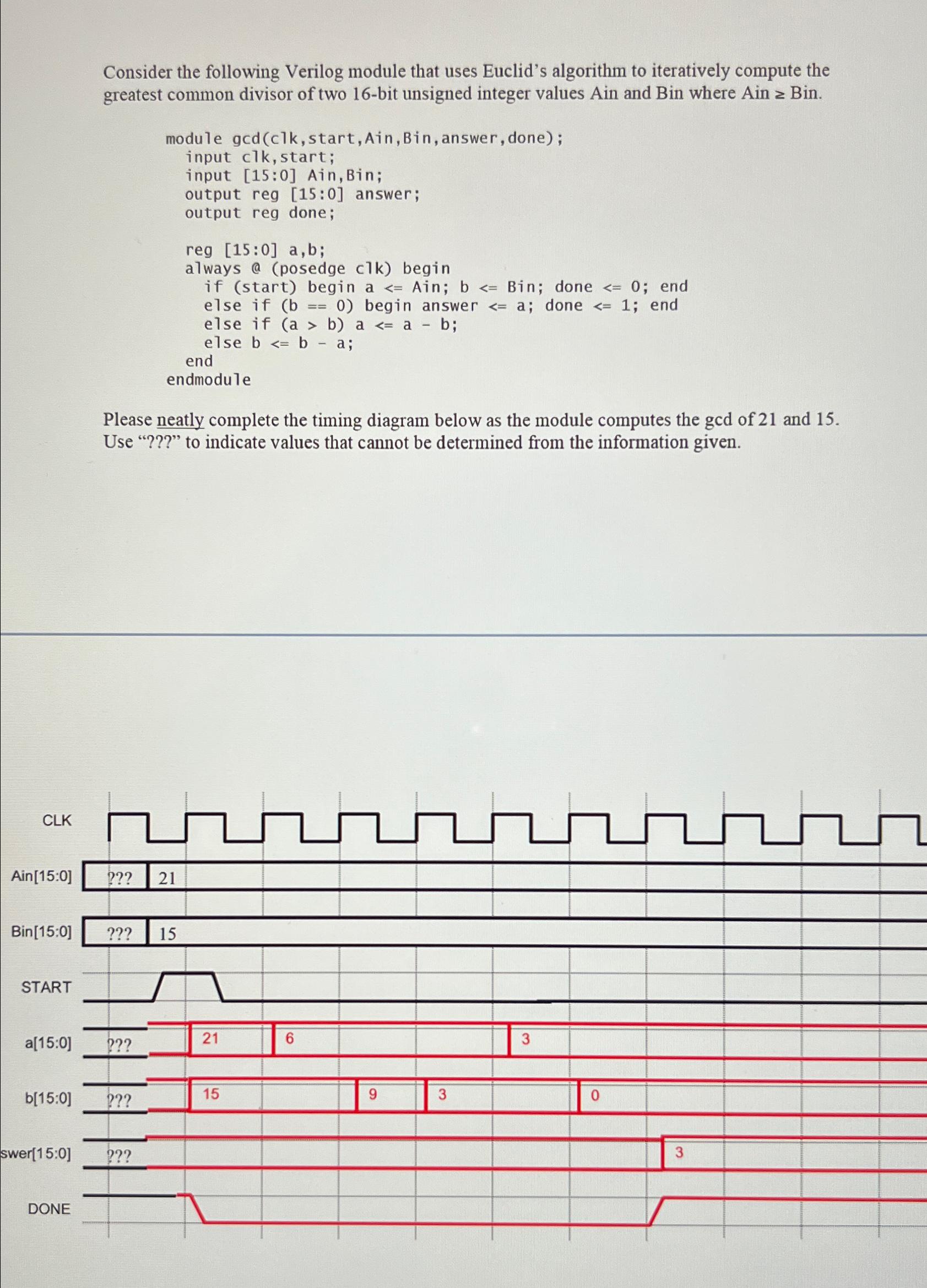

Consider the following Verilog module that uses Euclid's algorithm to iteratively compute the greatest common divisor of two 1 6 - bit unsigned integer values

Consider the following Verilog module that uses Euclid's algorithm to iteratively compute the greatest common divisor of two bit unsigned integer values Ain and Bin where Ain z Bin.

module gcdclkstart,Ain,Bin,answer, done;

input clkstart;

input : Ain, Bin;

output reg : answer;

output reg done;

reg:;

always @ posedge clk begin

if start begin Ain; Bin; done ; end

else if begin answer ; done ; end

else if ;

else ;

end

endmodule

Please neatly complete the timing diagram below as the module computes the ged of and Use to indicate values that cannot be determined from the information given.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started