Question

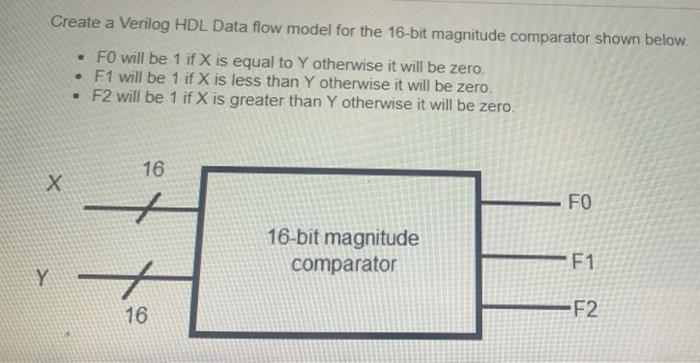

Create a Verilog HDL Data flow model for the 16-bit magnitude comparator shown below. .FO will be 1 if X is equal to Y

Create a Verilog HDL Data flow model for the 16-bit magnitude comparator shown below. .FO will be 1 if X is equal to Y otherwise it will be zero. .F1 will be 1 if X is less than Y otherwise it will be zero. F2 will be 1 if X is greater than Y otherwise it will be zero. 16 X Y 16 FO 16-bit magnitude comparator F1 F2

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Practical Business Statistics

Authors: Andrew Siegel

6th Edition

0123852080, 978-0123852083

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App