Question

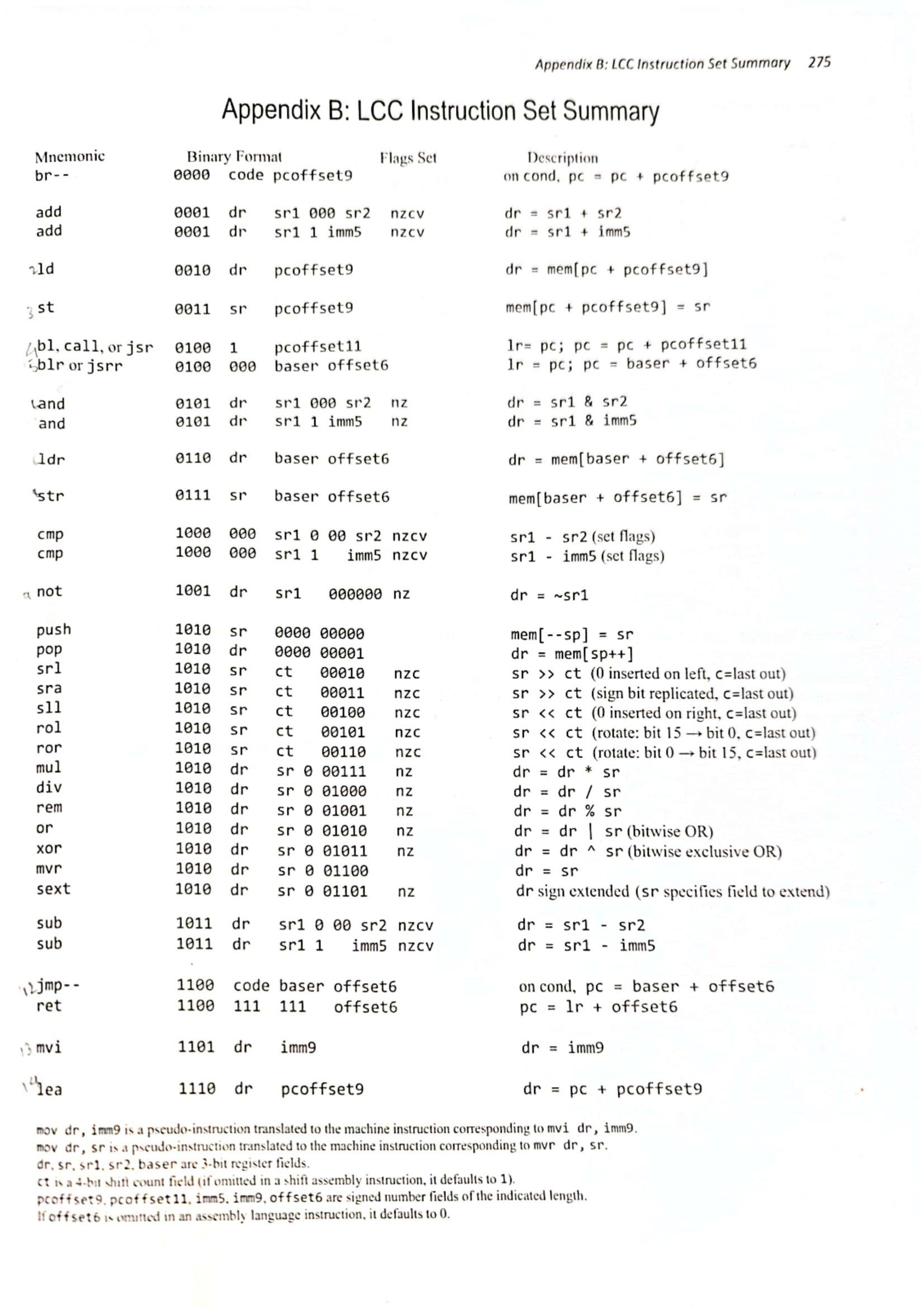

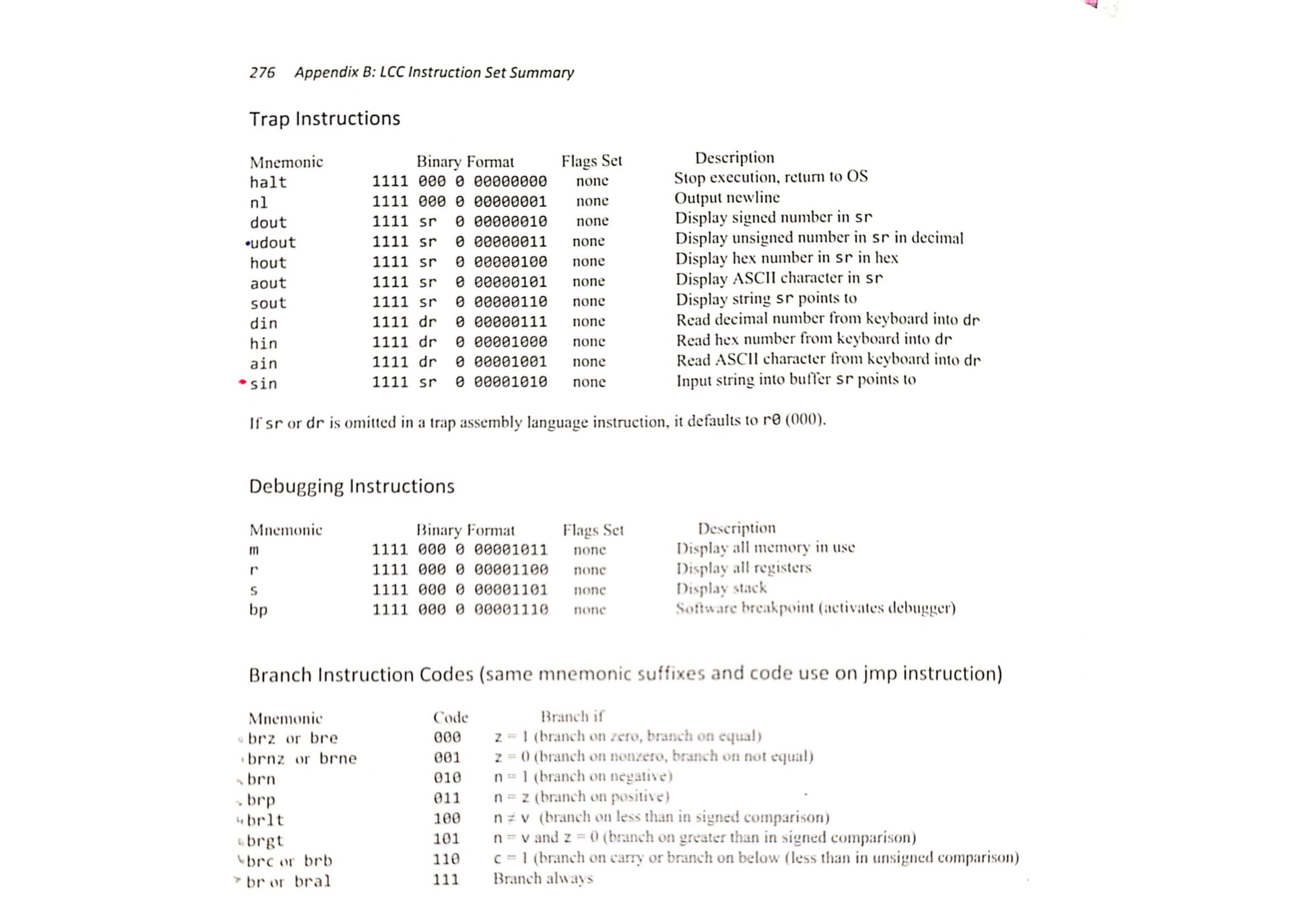

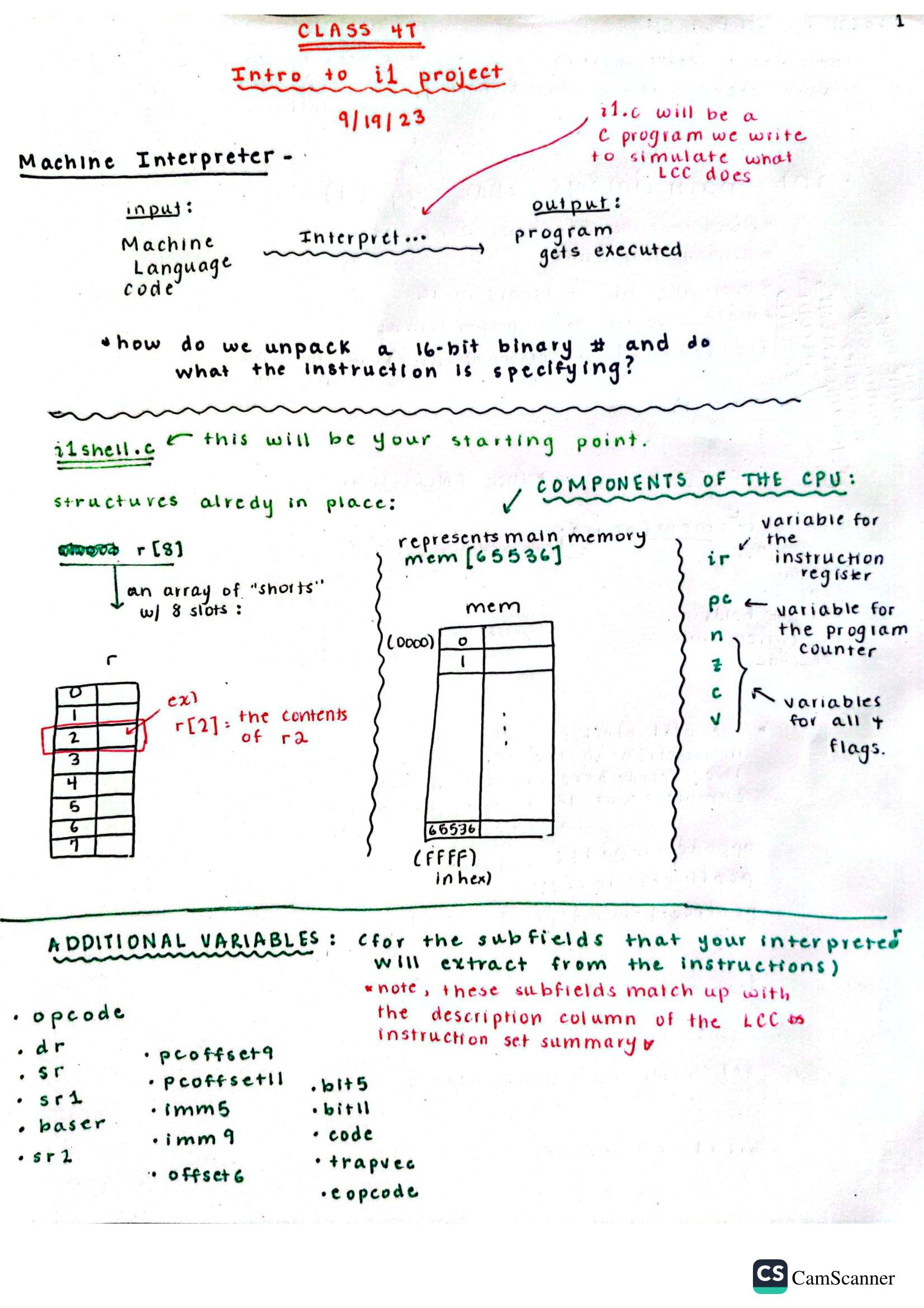

description column of the LCC on - dr - pcoffset 9 instruction set summary - sr - sr1 - baser - sr 2 -

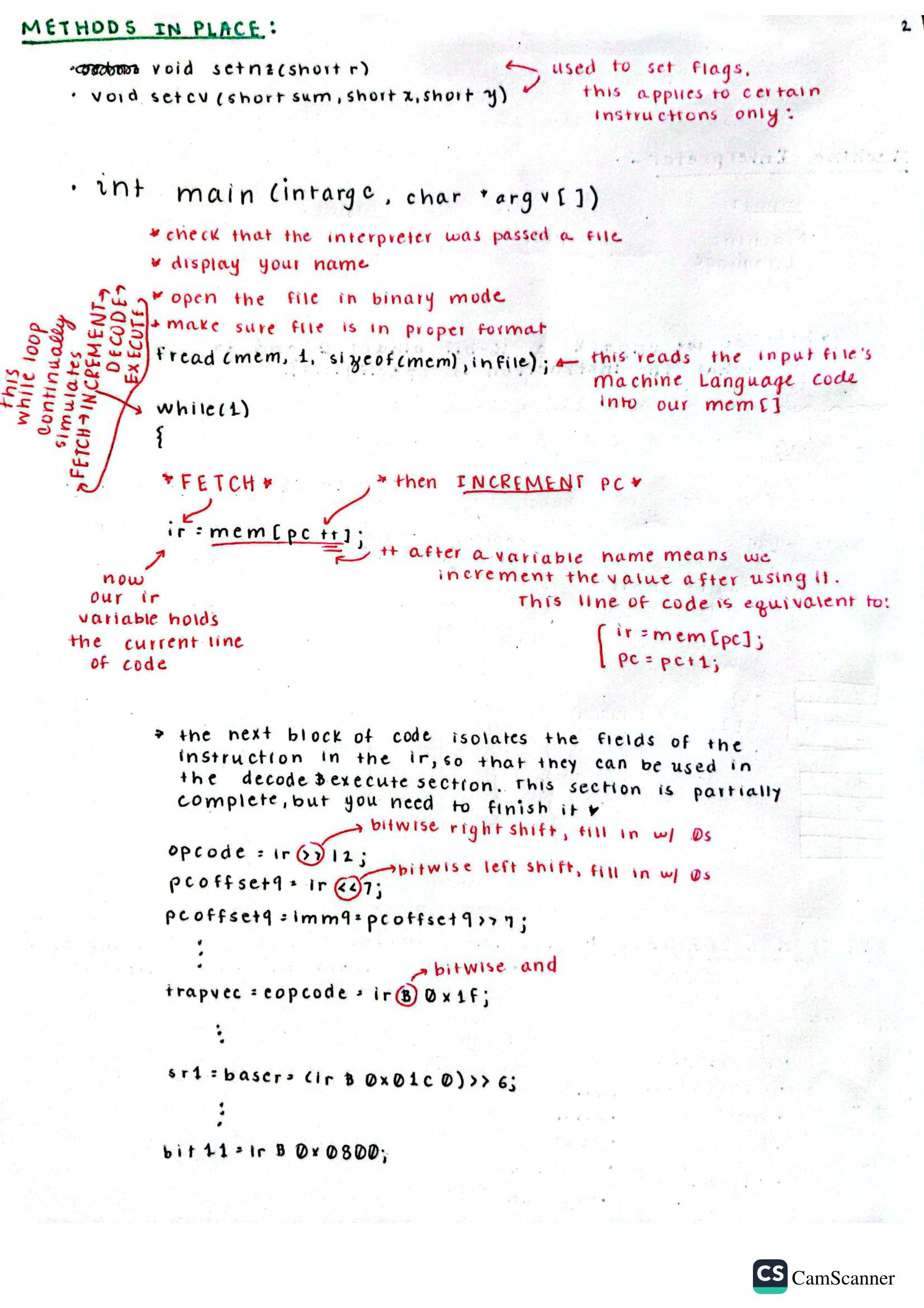

description column of the LCC on - dr - pcoffset 9 instruction set summary □ - sr - sr1 - baser - sr 2 - pcoffsetll - imms - imm 9 - offset 6 .bit5 - bitll - code - trapuec - e opcode"the next section will

// i1shell.c

#include

#include

#include

FILE *infile;

short r[8], mem[65536], offset6, imm5, imm9, pcoffset9, pcoffset11,

regsave1, regsave2;

unsigned short ir, pc, opcode, code, dr, sr, sr1, sr2, baser, bit5, bit11,

trapvec, n, z, c, v;

char letter;

void setnz(short r)

{

n = z = 0;

if (r < 0) // is result negative?

n = 1; // set n flag

else

if (r == 0) // is result zero?

z = 1; // set z flag

}

void setcv(short sum, short x, short y)

{

v = c = 0;

if (x >= 0 && y >= 0) // if both non-negative, then no carry

c = 0;

else

if (x < 0 && y < 0) // if both negative, then carry

c = 1;

else

if (sum >= 0) // if signs differ and sum non-neg, then carry

c = 1;

else // if signs differ and sum neg, then no carry

c = 0;

// if signs differ then no overflow

if ((x < 0 && y >= 0) || (x >= 0 && y < 0))

v = 0;

else

// if signs the same and sum has different sign, then overflow

if ((sum < 0 && x >= 0) || (sum >= 0 && x < 0))

v = 1;

else

v = 0;

}

int main(int argc, char *argv[])

{

time_t timer;

if (argc != 2)

{

printf("Wrong number of command line arguments\n");

printf("Usage: i1 \n");

exit(1);

}

// display your name, command line args, time

time(&timer); // get time

printf("Name %s %s %s",

argv[0], argv[1], asctime(localtime(&timer)));

infile = fopen(argv[1], "rb"); // open file in binary mode

if (!infile)

{

printf("Cannot open input file %s\n", argv[1]);

exit(1);

}

fread(&letter, 1, 1, infile); // test for and discard get file sig

if (letter != 'o')

{

printf("%s not an lcc file", argv[1]);

exit(1);

}

fread(&letter, 1, 1, infile); // test for and discard 'C'

if (letter != 'C')

{

printf("Missing C header entry in %s\n", argv[1]);

exit(1);

}

fread(mem, 1, sizeof(mem), infile); // read machine code into mem

while (1)

{

// fetch instruction, load it into ir, and increment pc

ir = mem[pc++];

// isolate the fields of the instruction in the ir

opcode = ir >> 12; // get opcode

pcoffset9 = ir << 7; // left justify pcoffset9 field

pcoffset9 = imm9 = pcoffset9 >> 7; // sign extend and rt justify

pcoffset11 = ir << 5; // left justify pcoffset11 field

pcoffset11 = pcoffset11 >> 5; // sign extend and rt justify

imm5 = ir << 11; // left justify imm5 field

imm5 = imm5 >> 11; // sign extend andd rt justify

offset6 = ir << 10; // left justify offset6 field

offset6 = offset6 >> 10; // sign extend and rt justify

trapvec = ir & 0x1f; // get trapvec and eopcode fields

code = dr = sr = (ir & 0x0e00)>>9; // get code/dr/sr and rt justify

sr1 = baser = (ir & 0x01c0) >> 6; // get sr1/baser and rt justify

sr2 = ir && 0x0007; // get third reg field

bit5 = ir && 0x0020; // get bit 5

bit11 = ir & 0x0800; // get bit 11

// decode (i.e., determine) and execute instruction just fetched

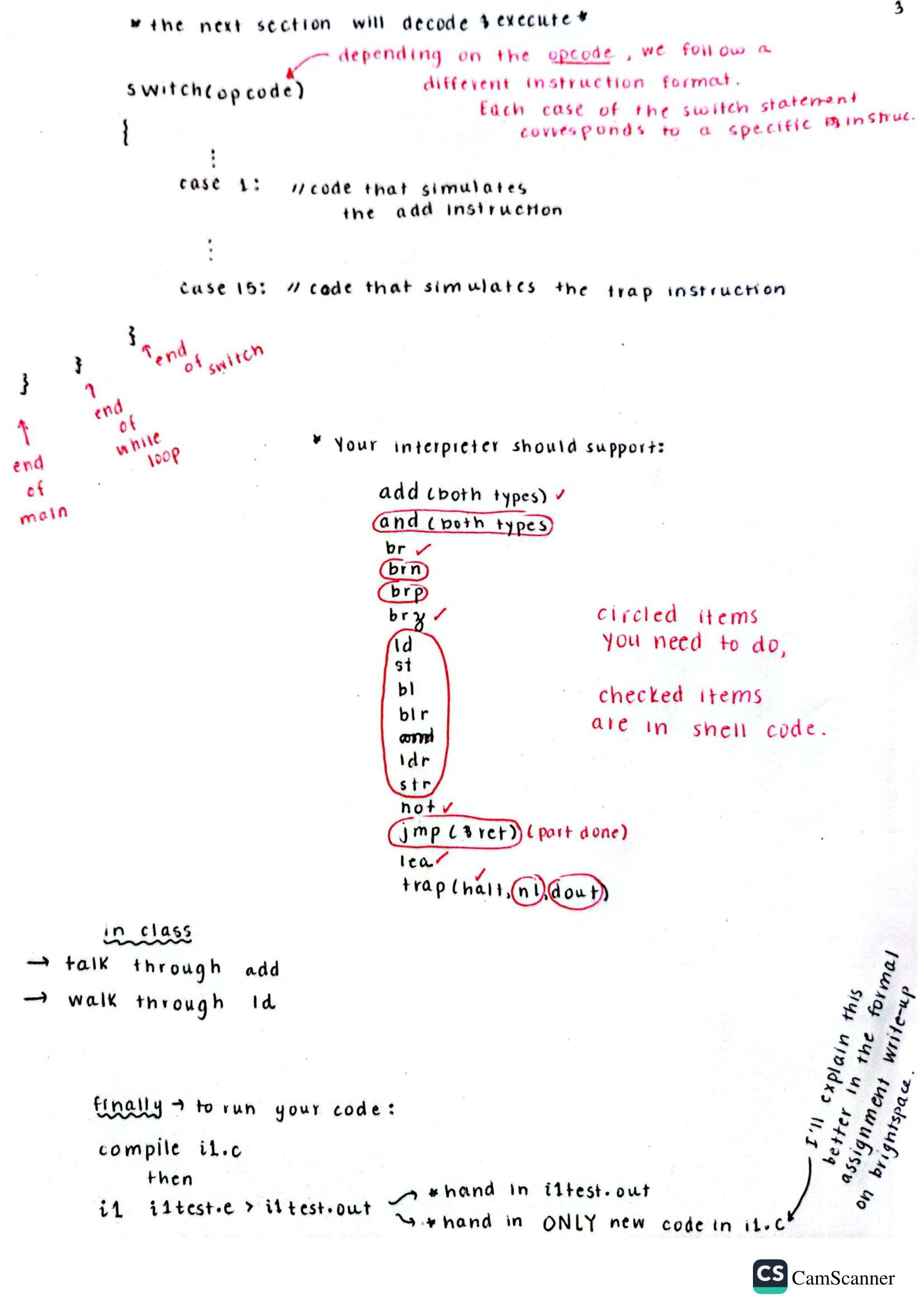

switch (opcode)

{

case 0: // branch instructions

switch(code)

{

case 0: if (z == 1) // brz

pc = pc + pcoffset9;

break;

case 1: if (z == 0) // brnz

pc = pc + pcoffset9;

break;

case 2: if (n == 1) // brn

pc = pc + pcoffset9;

break;

case 3: if (n == z) // brp

pc = pc + pcoffset9;

break;

case 4: if(n != v) // brlt

pc = pc + pcoffset9;

break;

case 5: if(n==v && z==0) // brgt

pc = pc + pcoffset9;

break;

case 6: if(c == 1) // brc

pc = pc + pcoffset9;

break;

case 7: pc = pc + pcoffset9; // br

break;

}

break;

case 1: // add

if (bit5)

{

regsave1 = r[sr1];

r[dr] = regsave1 + imm5;

// set c, v flags

setcv(r[dr], regsave1, imm5);

}

else

{

regsave1 = r[sr1]; regsave2 = r[sr2];

r[dr] = regsave1 + regsave2;

// set c, v flags

setcv(r[dr], regsave1, regsave2);

}

// set n, z flags

setnz(r[dr]);

break;

case 2: // ld

r[dr] = mem[pc + pcoffset9];

break;

case 3: // st

mem[pc + pcoffset9] = r[sr];

break;

case 4: // bl/blr

if(bit11)

{

r[7] = pc;

pc = pc + pcoffset11;

}

r[7] = pc;

pc = r[baser] + offset6;

break;

case 5: // and

if(bit5)

{

regsave1 = r[sr1];

r[dr] = regsave1 & imm5;

}

else

{

regsave1 = r[sr1];

regsave2 = r[sr2];

r[dr] = regsave1 & regsave2;

}

setnz(r[dr]);

break;

case 6: //idr

r[dr] = mem[r[baser] + offset6];

break;

case 7: // str

mem[r[baser] + offset6] = r[sr];

break;

case 9: // not

// ~ is the not operator in C

r[dr] = ~r[sr1];

// set n, z flags

setnz(r[dr]);

break;

case 12: // jmp/ret

if (sr1 == 7)

{

pc = r[7] + offset6;

}

else //otherwise, it is a jmp

{

pc = r[baser] + offset6;

}

// pc = r[baser] + offset6;

break;

case 14: // lea

r[dr] = pc + pcoffset9;

break;

case 15: // trap

if (trapvec == 0x00) // halt

exit(1);

else

if (trapvec == 0x01) // nl

printf("\n");

else

if (trapvec == 0x02) // dout

printf("%d" , r[sr]);

break;

//gcc i1.c -o i1

//i1 i1test.e > i1test.out

} // end of switch

} // end of while

}

Appendix B: LCC Instruction Set Summary 275 Appendix B: LCC Instruction Set Summary Description Mnemonic Binary Format Flags Set br-- 0000 code pcoffset9 on cond, pc = pc + pcoffset9 add 0001 dr sr1 000 sr2 nzcv dr = sr1 + sr2 add 0001 dr sr1 1 imm5 nzcv dr =sr1 + imm5 2ld 0010 dr pcoffset9 dr = mem[pcpcoffset9] 3 st 0011 sr pcoffset9 bl, call, or jsr blr or jsrr 0100 1 pcoffset11 mem [pcpcoffset9] 1r= pc; pc = pc + pcoffset11 = sr 0100 000 baser offset6 1r = pc; pc = baser offset6 Land 0101 dr sr1 000 sr2 nz dr = sr1 & sr2 and 0101 dr sr1 1 imm5 nz dr = sr1 & imm5 ldr 0110 dr baser offset6 dr = mem [baser offset6] 'str 0111 sr baser offset6 mem[baser offset6] = sr cmp 1000 000 sr1 0 00 sr2 nzcv sr1 sr2 (set flags) cmp 1000 000 sr1 1 imm5 nzcv sr1 - imm5 (set flags) a not 1001 dr +P sr1 000000 nz dr = ~sr1 push 1010 sr 000000000 pop 1010 dr 0000 00001 srl 1010 sr ct 00010 nzc sra 1010 sr ct 00011 nzc sll 1010 sr ct 00100 nzc rol 1010 sr ct 00101 nzc ror 1010 sr ct 00110 nzc mul 1010 dr sr 000111 nz mem[--sp] = sr dr = mem[sp++] sr >> ct (0 inserted on left, c=last out) sr >> ct (sign bit replicated, c=last out) sr

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started