Answered step by step

Verified Expert Solution

Question

1 Approved Answer

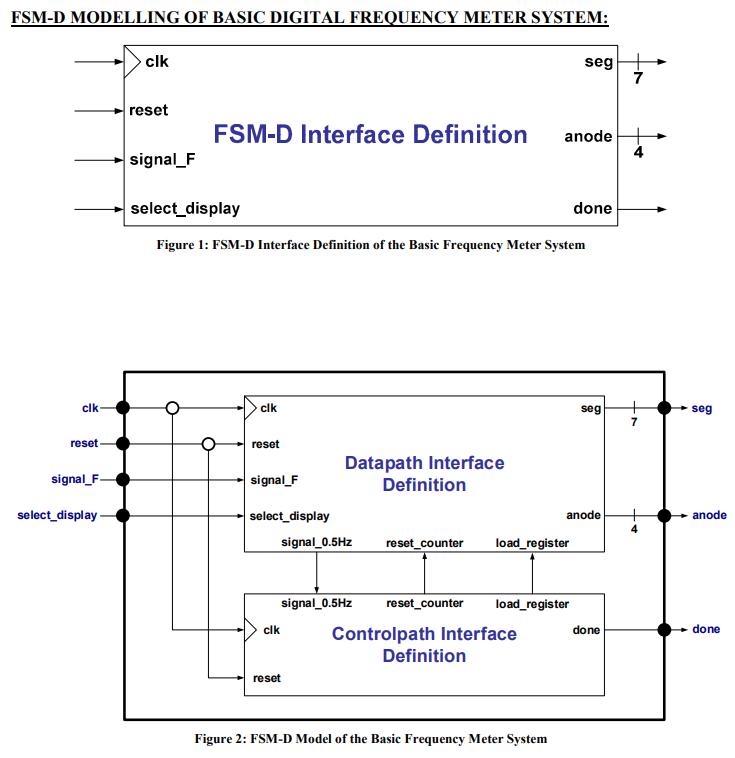

Design & construct a Digital Frequency Meter for implementation on the SPARTAN-6 XC6SLX16-3CSG324 FPGA using VHDL. The Digital Frequency Meter System must utilize Pulse Counting

Design & construct a Digital Frequency Meter for implementation on the SPARTAN-6 XC6SLX16-3CSG324 FPGA using VHDL.

The Digital Frequency Meter System must utilize Pulse Counting and be capable of measuring the frequency of input square waveforms originating from the selected programmable logic device for the range 0Hz – 10kHz, with a resolution of 1Hz. Required to verify their system via Xilinx ISE.

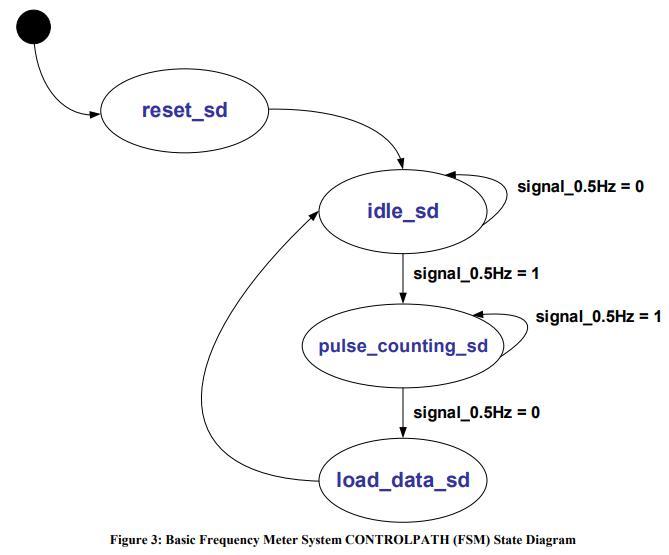

The datapath and control path are shown below:

FSM-D MODELLING OF BASIC DIGITAL FREQUENCY METER SYSTEM: clk reset signal_F. select_display- clk reset signal_F FSM-D Interface Definition anode select_display Figure 1: FSM-D Interface Definition of the Basic Frequency Meter System clk reset signal_F select_display signal_0.5Hz Datapath Interface Definition clk reset signal_0.5Hz reset_counter load_register reset_counter load_register Controlpath Interface seg Definition Figure 2: FSM-D Model of the Basic Frequency Meter System done anode seg done 7 4 7 seg anode done

Step by Step Solution

★★★★★

3.37 Rating (163 Votes )

There are 3 Steps involved in it

Step: 1

Solution library IEEE use IEEESTDLOGIC1164ALL use IEEESTDLOGICUNSIGNEDALL Uncomment the following li...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started