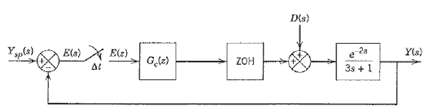

Question: The block diagram of a digital control system is shown in Fig. The sampling period is ?t 1 min.(a) Design the digital controller Gc(z) so

The block diagram of a digital control system is shown in Fig. The sampling period is ?t 1 min.(a) Design the digital controller Gc(z) so that the closed-loop system exhibits a first-order response to a unit step change in the set point (after an appropriate lime delay).(b) Will this controller eliminate offset after a step change in the set point? Justify your answer.(c) Is the controller physically realizable? Justify your answer.(d) Design a digital PID controller based on the ITAE (set-point) method in Chapter 12 and examine its performance for a step change in set point. Approximate the sampler and zero-order- hold by a time delay of ? ?t/2.

Ds) Yla) Ela) Ele) Y(s) 3s +1 G,le) ZOH

Step by Step Solution

3.35 Rating (170 Votes )

There are 3 Steps involved in it

a The closedloop response for setpoint changes is We want the closedloop system exhibits a fir... View full answer

Get step-by-step solutions from verified subject matter experts

Document Format (1 attachment)

38-E-C-E-P-C (278).docx

120 KBs Word File