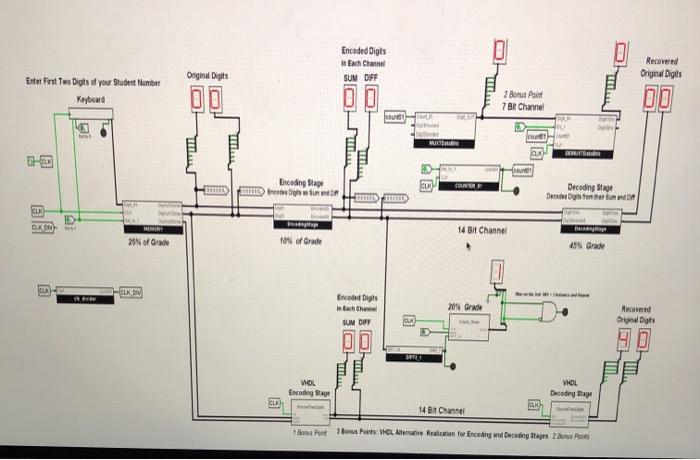

Design Specifications: Design a digital system with the following functionality: You will type the first two digits of your student number (you will also experiment with other digits) using your own keyboard and the Logisim keyboard block. Each digit will be converted to a 7 bit ascii representation by the Logisim keyboard. You should encode the two digits typed in your keyboard as their sum and their difference. You will send the encoded version (sum and diff) of the two digits, simultaneously, through a 14 bit channel (35% of grade up to this part). At the other end of the channel you will decode the originals digits of you student number from the arriving sum and difference of such digits (this particular part is 45 % of your grade). In addition, when experimenting with streams of different digits typed at the keyboard, a blue light should be turned on after two instances, consecutive or not consecutive, where the difference between the digits was 3. The blue light will remain on until another instance of 3, being the difference between the digits, occurs. It will basically count two instances of the difference between digits being 3 and will repeat the count (20% of grade). The keyboard will be used in Logisim as it was shown in class or in the class videos. A demonstration video of what is expected will also be made available in the Project Folder in Blackboard. Constraint: Do not use more than 5 Flip Flops. You may use Logisim blocks for arithmetic operations or you can design you own sub-circuits. VHDL Bonuses (all bonus points are over the final course grade): A VHDL realization of the encoding stage that outputs the sum and difference of the first two digits is worth 1 Bonus Point. A VHDL realization of the decoding stage that recovers the original digits from their sum and difference is worth 2 Bonus Points. Other Bonus: A Multiplexer-Demultiplexer design that allows to transmit one digit at a time over a 7 bit channel (instead of two digits simultaneously over a 14 bit channel) is worth 2 Bonus Points. Note that after the multiplexed channel you should be able to inject the digits in the same decoding block used for the 14 bit channel. This is worth 2 Bonus points. A possible architecture of your system, using different subsystems, is depicted in the next page. Encoded Digts In Each Channel SUM DIFF Recovered Original Digits Original Digits Enter Fest Two Diots of your Student Number Keyboard 2 Borut Paw 7 B Channel DEM PC MOBI CRM Bahn Encoding stage Treba CUKU COUNTA Decoding Stage Designer ind of CU OM 14 Bit Channel 25% of Grade Nos of Grade 45 Grade OUR EUX ON Encoded Digits inch Chaw 20% Grade covered Originals SUM DRY 90 DAT TI VOL Encoding Rage LE VOL Decoding age 14 Bt Channel Borut Port Bonus Ponte VHOL A Bratton for Encoding and Decodig fragt Bonus Formal Report Requirements: Describe, at a system block-level, the general design architecture that gives the desired functionality. Before performing the actual circuit synthesis, describe the functionality of every subsystem used in your design. Perform the circuit synthesis for each subsystem. Use LOGISIM (required) to run a simulation of the overall design and verify that your design logic works as intended. Try to conceptualize possible alternative designs and their capacity to meet the design specifications and constraints. Design Specifications: Design a digital system with the following functionality: You will type the first two digits of your student number (you will also experiment with other digits) using your own keyboard and the Logisim keyboard block. Each digit will be converted to a 7 bit ascii representation by the Logisim keyboard. You should encode the two digits typed in your keyboard as their sum and their difference. You will send the encoded version (sum and diff) of the two digits, simultaneously, through a 14 bit channel (35% of grade up to this part). At the other end of the channel you will decode the originals digits of you student number from the arriving sum and difference of such digits (this particular part is 45 % of your grade). In addition, when experimenting with streams of different digits typed at the keyboard, a blue light should be turned on after two instances, consecutive or not consecutive, where the difference between the digits was 3. The blue light will remain on until another instance of 3, being the difference between the digits, occurs. It will basically count two instances of the difference between digits being 3 and will repeat the count (20% of grade). The keyboard will be used in Logisim as it was shown in class or in the class videos. A demonstration video of what is expected will also be made available in the Project Folder in Blackboard. Constraint: Do not use more than 5 Flip Flops. You may use Logisim blocks for arithmetic operations or you can design you own sub-circuits. VHDL Bonuses (all bonus points are over the final course grade): A VHDL realization of the encoding stage that outputs the sum and difference of the first two digits is worth 1 Bonus Point. A VHDL realization of the decoding stage that recovers the original digits from their sum and difference is worth 2 Bonus Points. Other Bonus: A Multiplexer-Demultiplexer design that allows to transmit one digit at a time over a 7 bit channel (instead of two digits simultaneously over a 14 bit channel) is worth 2 Bonus Points. Note that after the multiplexed channel you should be able to inject the digits in the same decoding block used for the 14 bit channel. This is worth 2 Bonus points. A possible architecture of your system, using different subsystems, is depicted in the next page. Encoded Digts In Each Channel SUM DIFF Recovered Original Digits Original Digits Enter Fest Two Diots of your Student Number Keyboard 2 Borut Paw 7 B Channel DEM PC MOBI CRM Bahn Encoding stage Treba CUKU COUNTA Decoding Stage Designer ind of CU OM 14 Bit Channel 25% of Grade Nos of Grade 45 Grade OUR EUX ON Encoded Digits inch Chaw 20% Grade covered Originals SUM DRY 90 DAT TI VOL Encoding Rage LE VOL Decoding age 14 Bt Channel Borut Port Bonus Ponte VHOL A Bratton for Encoding and Decodig fragt Bonus Formal Report Requirements: Describe, at a system block-level, the general design architecture that gives the desired functionality. Before performing the actual circuit synthesis, describe the functionality of every subsystem used in your design. Perform the circuit synthesis for each subsystem. Use LOGISIM (required) to run a simulation of the overall design and verify that your design logic works as intended. Try to conceptualize possible alternative designs and their capacity to meet the design specifications and constraints