Question

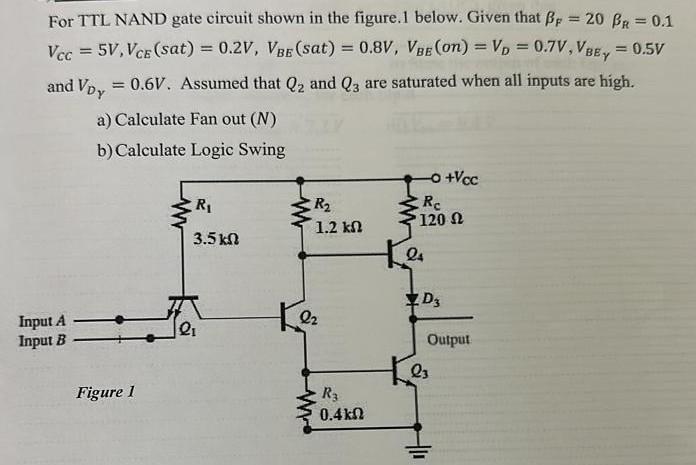

For TTL NAND gate circuit shown in the figure. 1 below. Given that p = 20 BR = 0.1 Vcc= 5V, VCE (sat) =

For TTL NAND gate circuit shown in the figure. 1 below. Given that p = 20 BR = 0.1 Vcc= 5V, VCE (sat) = 0.2V, VBE (Sat) = 0.8V, VBE (on) = VD = 0.7V,VBEY = 0.5V and Voy = 0.6V. Assumed that Q and Q3 are saturated when all inputs are high. Input A Input B a) Calculate Fan out (N) b) Calculate Logic Swing Figure 1 R 3.5 kn Q R 1.2 Ke R3 0.4 -o +Vcc Re 120 Kes D3 Output 03

Step by Step Solution

3.44 Rating (154 Votes )

There are 3 Steps involved in it

Step: 1

To calculate the fan out N and the logic swing in the TTL NAND gate circuit we need to analyze the c...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Management Accounting

Authors: Leslie G. Eldenburg, Albie Brooks, Judy Oliver, Gillian Vesty, Rodney Dormer, Vijaya Murthy, Nick Pawsey

4th Edition

0730369382, 978-0730369387

Students also viewed these Marketing questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App