Answered step by step

Verified Expert Solution

Question

1 Approved Answer

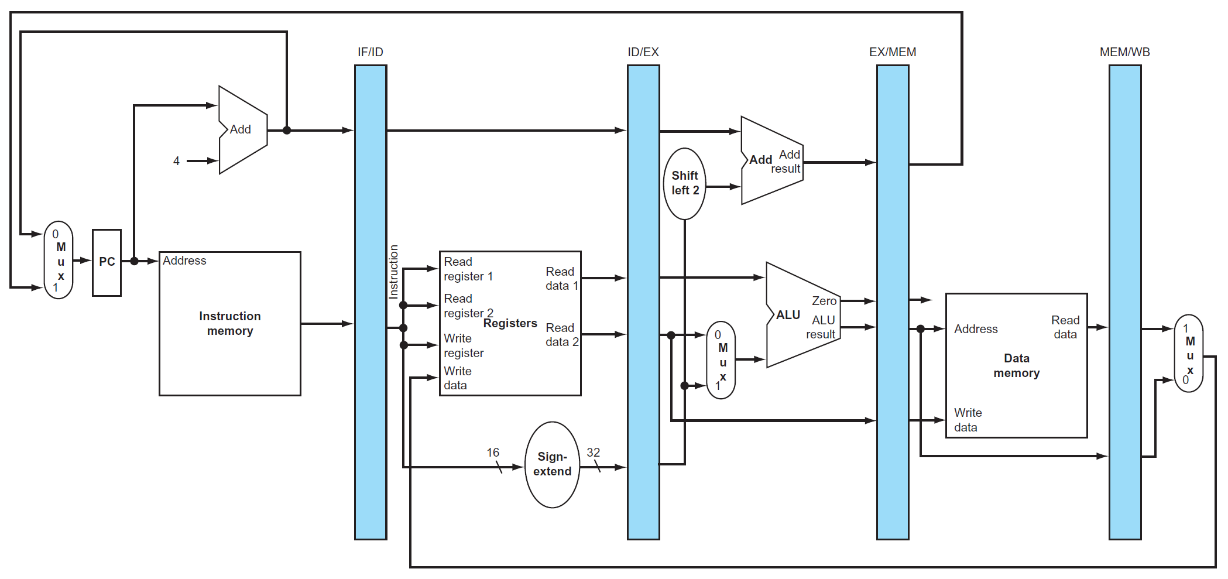

Examine how latencies of individual components of the datapath affect the clock cycle time of the entire datapath, and how these components are utilized by

Examine how latencies of individual components of the datapath affect the clock cycle time of the entire datapath, and how these components are utilized by instructions

| I-Mem | Add | Mux | ALU | Regs | D-Mem | Sign-Ext | Shift Left |

| |

| ps | 230 | 80 | 20 | 100 | 95 | 270 | 15 | 10 |

|

requirement:

- What is the clock cycle time if the only types of instructions we need to support are ALU instructions (ADD, AND, etc.)?

- What is the clock cycle time if we only have to support LW instructions?

- What is the clock cycle time if we must support ADD, BEQ, LW, and SW instructions?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started