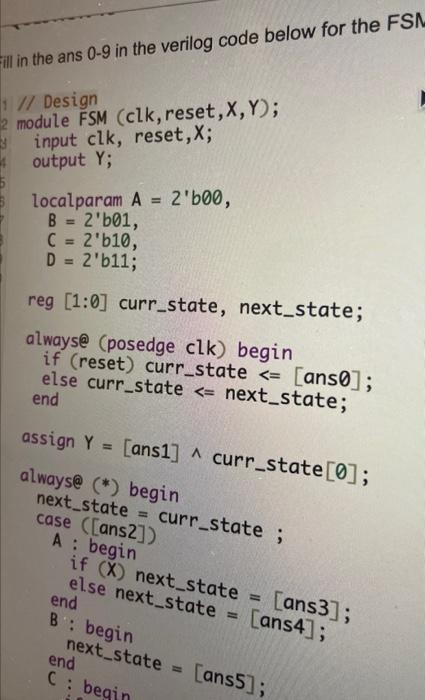

Question: Fill in the ans 0-9 in the verilog code below for the FSM 1 // Design 2 module FSM (clk, reset, X, Y); input

![CAS case A: begin if (X) next_state = [ans3]; else next_state = [ans4]; end B: begin next_state= [ans5]; end](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/answers/2023/10/65213f91b1aec_77765213f91ad19c.jpg)

Fill in the ans 0-9 in the verilog code below for the FSM 1 // Design 2 module FSM (clk, reset, X, Y); input clk, reset, X; output Y; localparam A = 2'b00, B = 2'b01, (= 2 b10, D = 2'b11; reg [1:0] curr_state, next_state; always@ (posedge clk) begin if (reset) curr_state CAS case A: begin if (X) next state = [ans3]; else next_state = [ans4]; end B: begin next_state= [ans5]; end C: begin if (X) next_state = [ans6]; else next_state = [ans7]; end D: begin if (X) next_state = [ans8]; else next_state = [ans9]; end endcase end endmodule e and Submit to , ans1 = ans3 = , ans5 = 1 , ans7 = ans9 =

Step by Step Solution

3.42 Rating (161 Votes )

There are 3 Steps involved in it

ans0 In Verilog whe... View full answer

Get step-by-step solutions from verified subject matter experts